## Black/White Pattern Generator PM 5540

9449 055 40...1

9499 490 04311

1/971/2/02-08

# **PHILIPS**

operating and service manual

## **Contents**

| Genera                 | Intermation                                | Page | Service | instructions     |                            | r'age |

|------------------------|--------------------------------------------|------|---------|------------------|----------------------------|-------|

| l.                     | Introduction                               | 5    | IX.     | UNIT 1           | The power supply unit      | 32    |

| II.                    | Technical data                             | 6    | X.      | UNIT 3 and 4     | The circle register        | 40    |

| III.                   | Accessories                                | 7    | XI.     | UNIT 5           | The memory                 | 54    |

| IV.                    | Description of simplified block-diagram    | 8    | XII.    | UNIT 6           | The line decoder           | 64    |

|                        |                                            |      | XIII.   | UNIT 7           | The line selector register | 72    |

| Operating instructions |                                            |      | XIV.    | UNIT 8           | The interval decoder       | 82    |

| V.                     | Installation                               | 11   | XV.     | UNIT 9           | The horizontal decoder     | 94    |

|                        | A. Adjusting to the local mains voltage    | 11   | XVI.    | UNIT 10          | The horizontal divider     | 108   |

|                        | B. Earthing                                | 12   | XVII.   | UNIT 11          | The vertical decoder       | 118   |

|                        | C. Mounting in a 19" rack                  | 12   | XVIII.  | UNIT 12          | The vertical divider       | 128   |

| VI.                    | Survey of controls and sockets             | 14   | XIX.    | UNIT 13          | The black and white steps  | 140   |

|                        | A. Front of the instrument                 | 15   | XX.     | UNIT 14          | The linear gate            | 152   |

|                        | B. Rear of the instrument                  | 16   | XXI.    | UNIT 15          | The cross-bar gate         | 164   |

|                        | <ul><li>C. Changing testpatterns</li></ul> | 17   | XXII.   | UNIT 16          | The output amplifiers      | 174   |

|                        | D. Connections                             | 17   | XXIII.  | UNIT 17          | The input amplifiers       | 180   |

| VII.                   | The principle of the circle generator      | 18   | XXIV.   | UNIT 18          | The connection board       | 190   |

|                        | A. Circle register                         | 19   | XXV.    | Description of   | basic circuits             | 191   |

|                        | B. The memory                              | 19   | XXVI.   | Access to and    | replacement of parts       | 199   |

|                        | C. Line-selector register                  | 19   | XXVII.  | Maintenance      |                            | 201   |

|                        | D. Interval selector                       | 19   | XXVIII. | List of mechar   | nical parts                | 202   |

| VIII.                  | Description of detailed block-diagram      | 25   | XXIX.   | List of electric | al parts                   | 204   |

|                        | A. Input amplifiers                        | 25   | XXX.    | Sales and ser    | vice all over the world    | 210   |

|                        | B. Pulse generators                        | 25   |         |                  |                            |       |

|                        | C. Pattern generators                      | 25   |         |                  |                            |       |

|                        | D. Output amplifiers                       | 26   |         |                  |                            |       |

## List of figures

|             |                                         |    | •          |        |                                              |     |

|-------------|-----------------------------------------|----|------------|--------|----------------------------------------------|-----|

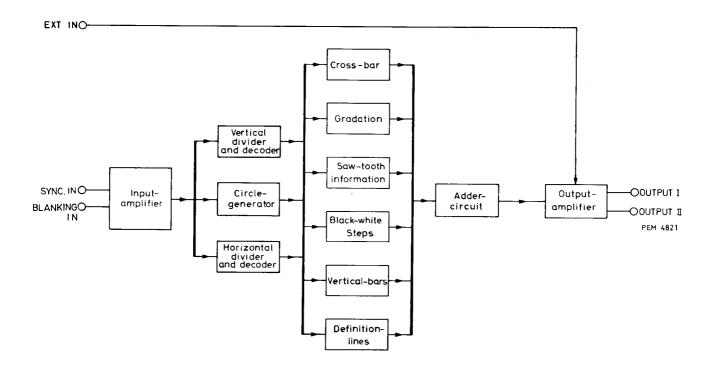

| Fig. IV-1   | Simplified block-diagram                | 9  | Fig. XIII- | -2 F   | Pulse generator, pre-selector of line        |     |

| Fig. V-1    | Front view of the instrument            | 11 |            | r      | egister                                      | 73  |

| Fig. V-2    | Rear view of the instrument             | 12 | Fig. XIII- | -3 E   | Block-diagram, line register                 | 74  |

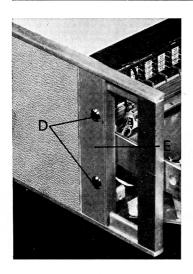

| Fig. V-3    | Side view                               | 13 | Fig. XIII- | -4a P  | Printed wiring board, line register          |     |

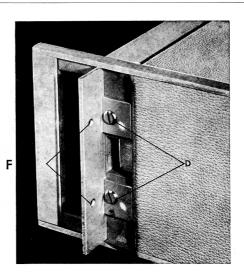

| Fig. V-4    | Side view                               | 13 |            | (4     | A version)                                   | 75  |

| Fig. VI-1   | Front view of the instrument            | 14 | Fig. XIII- | -4b P  | Printed wiring board, line register          |     |

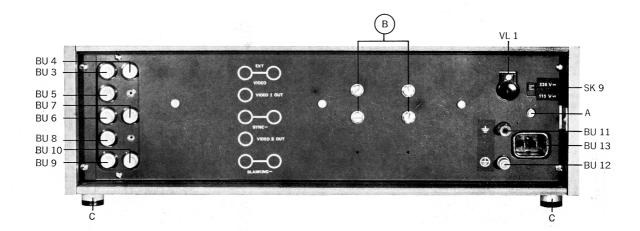

| Fig. VI-2   | Rear view of the instrument             | 16 |            | (1     | E version)                                   | 77  |

| Fig. VII-1  | Principe of the circle generator        | 18 | Fig. XIII- | -5 C   | Circuit diagram, line register               | 79  |

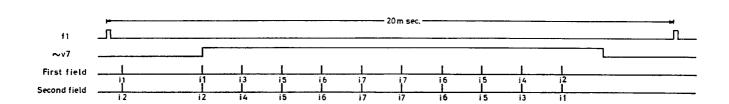

| Fig. VII-2  | Intervals of the two fields             | 18 | Fig. XIV-  | '-1 C  | Oscillograms, Unit 8                         | 82  |

| Fig. VIII-1 | Detailed block-diagram                  | 22 | Fig. XIV-  | '-2 P  | Pulse diagram for ''q1''                     | 83  |

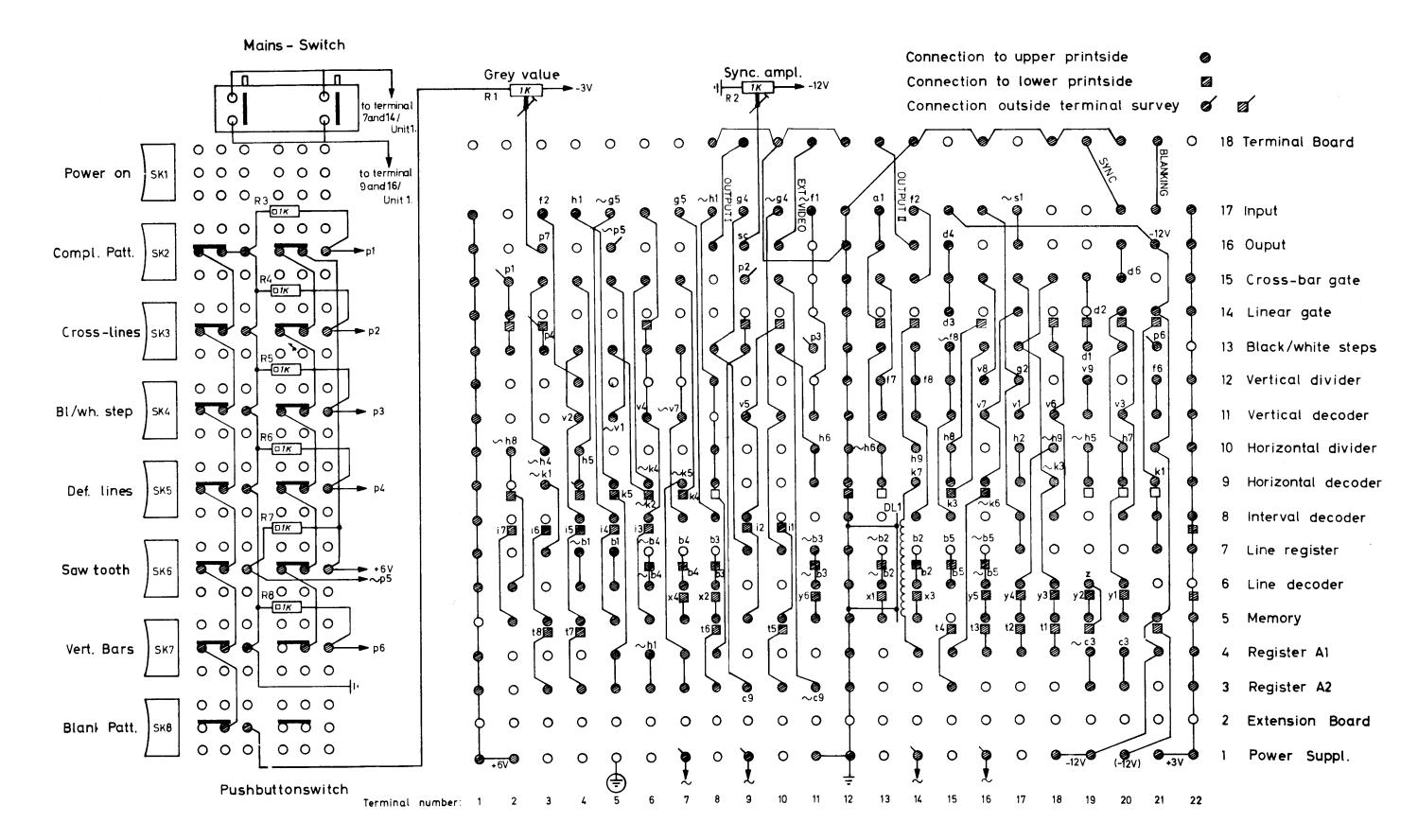

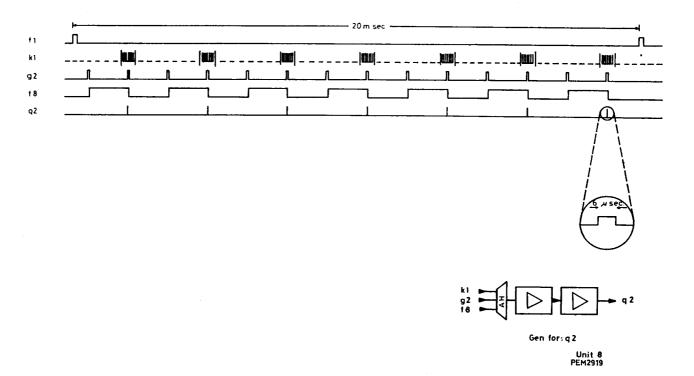

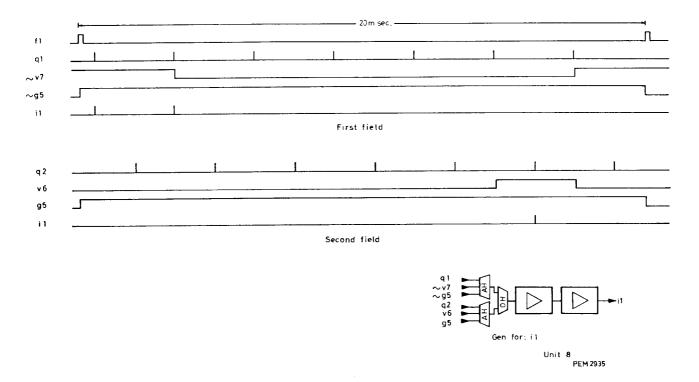

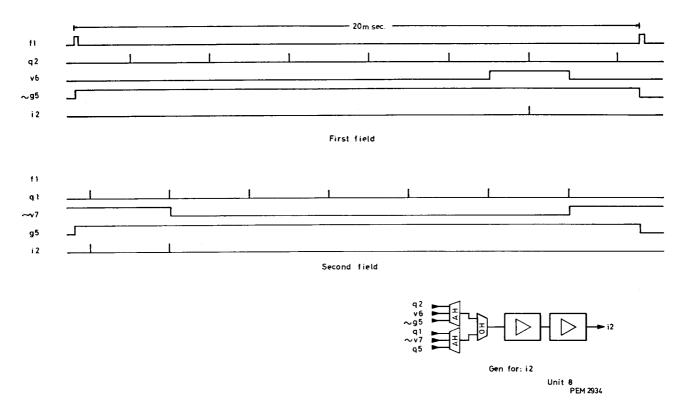

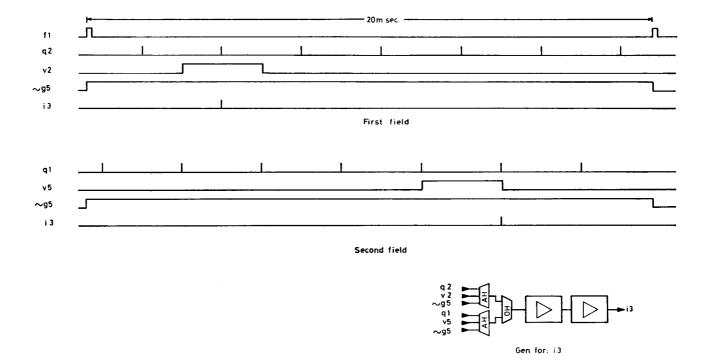

| Fig. IX-1   | Connection-terminal blocks              | 29 | Fig. XIV-  | '-3 P  | Pulse diagram for ''q2''                     | 83  |

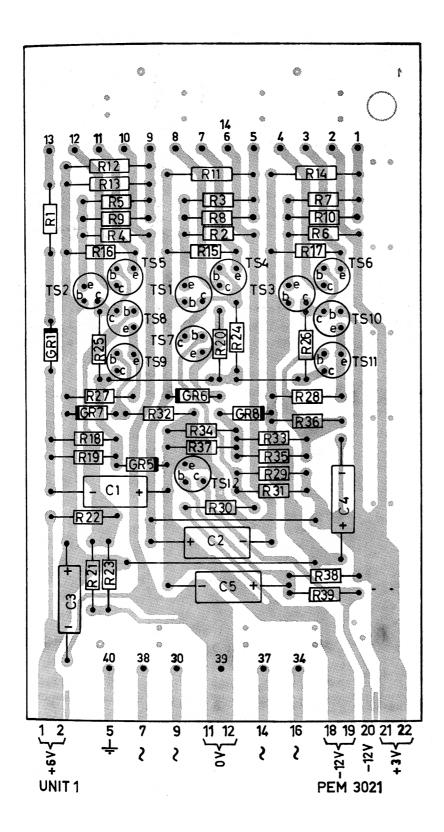

| Fig. IX-2   | Printed wiring board, Unit 1            | 33 | Fig. XIV-  | '-4 P  | Pulse diagram for ''i1''                     | 84  |

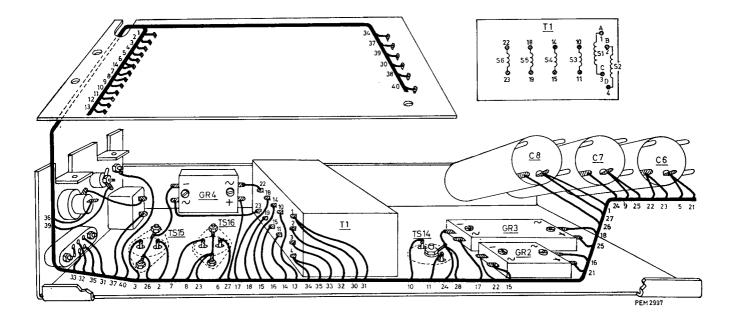

| Fig. IX-3   | Wiring power-supply                     | 34 | Fig. XIV-  | ′-5 P  | Pulse diagram for ''i2''                     | 84  |

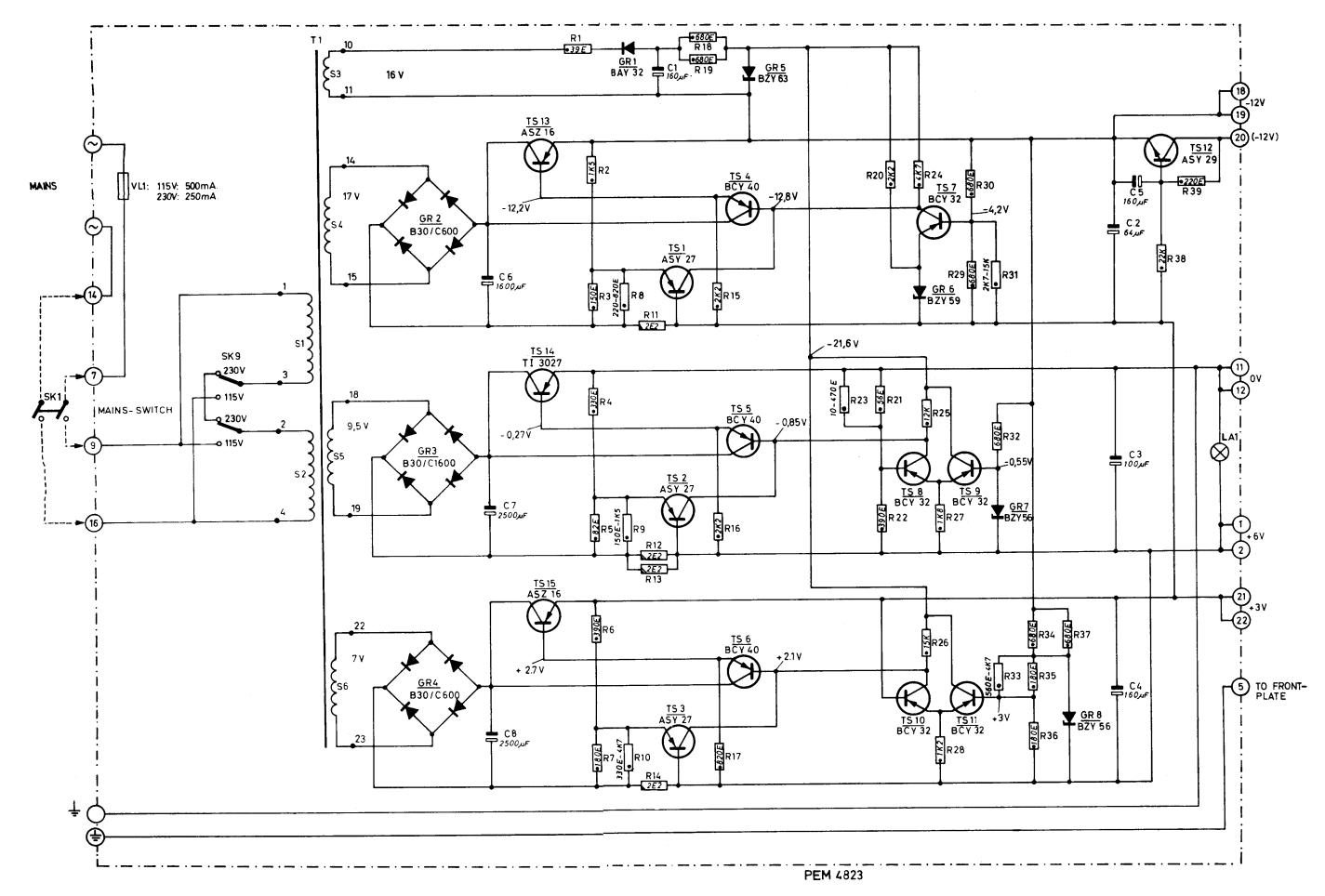

| Fig. IX-4   | Circuit diagram, power-supply unit      | 36 | Fig. XIV-  | '-6 P  | Pulse diagram for ''i3''                     | 85  |

| Fig. X-1    | Circle                                  | 41 | Fig. XIV-  | '-7 P  | Pulse diagram for "i4"                       | 85  |

| Fig. X-2    | Pulse diagram                           | 41 | Fig. XIV-  | '-8 P  | Pulse diagram for ''i5''                     | 86  |

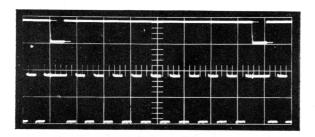

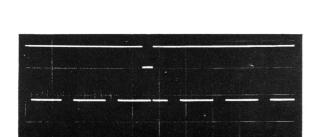

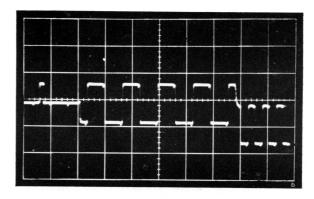

| Fig. X-3    | Oscillograms, Units 3 and 4             | 42 | Fig. XIV-  | -9 P   | Pulse diagram for ''i6''                     | 86  |

| Fig. X-4    | Block-diagram, counting register        | 43 | Fig. XIV-  | -10 P  | Pulse diagram for "i7"                       | 87  |

| Fig. X-5    | Printed wiring board, counting register | 44 | Fig. XIV-  | -11 A  | Arrangement of i-pulses                      | 87  |

| Fig. X-6    | Circuit diagram, counting register      | 46 | Fig. XIV-  | '-12 B | Block-diagram, interval decoder              | 88  |

| Fig. X-7    | Block-diagram, circle register          | 48 | Fig. XIV-  |        | Printed wiring board, interval decoder       | 89  |

| Fig. X-8    | Printed wiring board, circle register   | 49 | Fig. XIV-  | ′-14 C | Circuit diagram, interval decoder            | 91  |

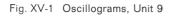

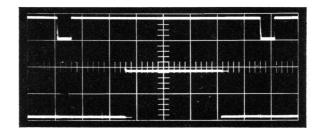

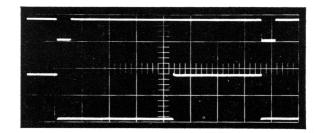

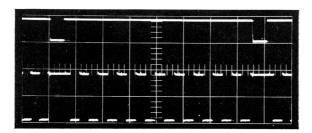

| Fig. X-9    | Circuit diagram, circle register        | 51 | Fig. XV-1  | -1 C   | Oscillograms, Unit 9                         | 95  |

| Fig. XI-1   | Principle of the memory                 | 55 | Fig. XV-2  | .2 P   | Pulse diagrams for ''k4'' and '' $\sim$ k4'' | 97  |

| Fig. XI-2   | Wiring diagram of memory                | 56 | Fig. XV-3  |        | Pulse diagrams for ''k3'' and '' $\sim$ k3'' | 97  |

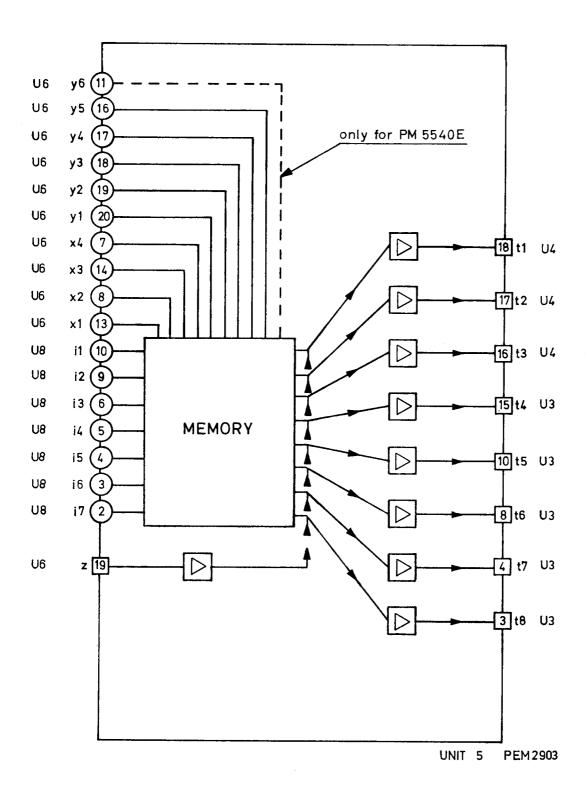

| Fig. XI-3   | Block-diagram, memory                   | 57 | Fig. XV-4  | 4 P    | Pulse diagrams for ''k2'' and '' $\sim$ k2'' | 98  |

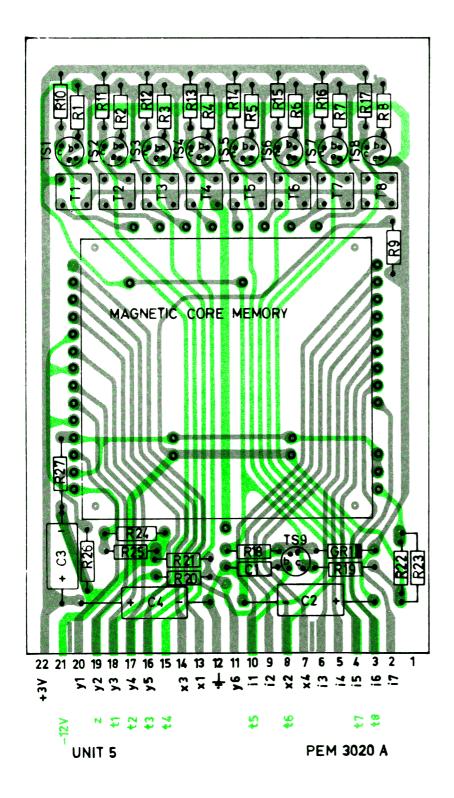

| Fig. XI-4a  | Printed wiring board, memory            |    | Fig. XV-5  | .5 P   | Pulse diagrams for ''k1'' and '' $\sim$ k1'' | 98  |

|             | (A version)                             | 58 | Fig. XV-6  | -6 P   | Pulse diagrams for ''k5'' and '' $\sim$ k5'' | 99  |

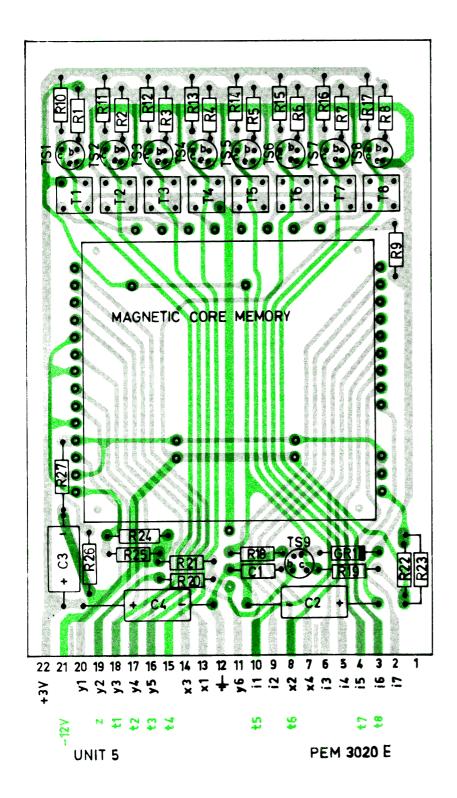

| Fig. XI-4b  | Printed wiring board, memory            |    | Fig. XV-7  | .7 P   | Pulse diagram for '' $\sim$ k6''             | 99  |

|             | (E version)                             | 59 | Fig. XV-8  |        |                                              | 100 |

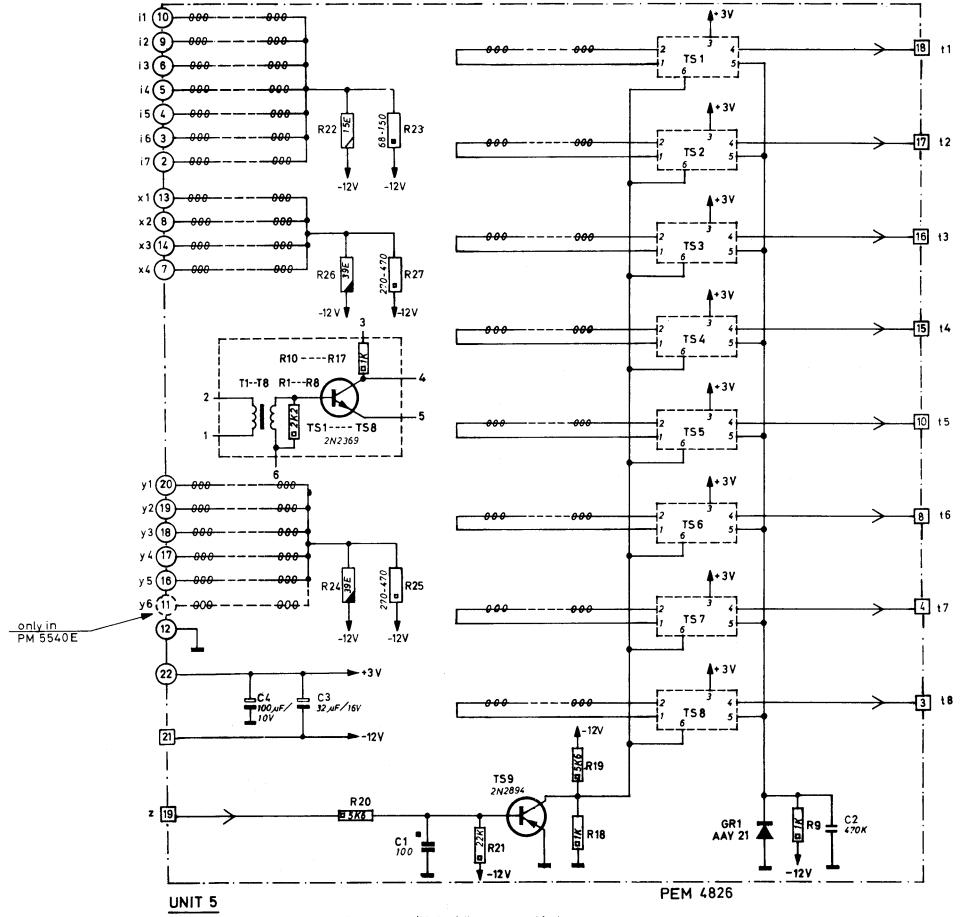

| Fig. XI-5   | Circuit diagram, memory                 | 61 | Fig. XV-9  | .9 P   | Pulse diagram for "h3"                       | 100 |

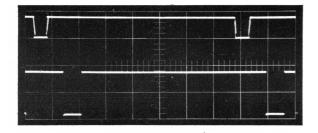

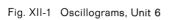

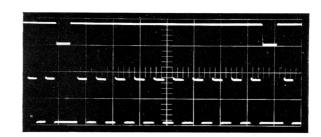

| Fig. XII-1  | Oscillograms, Unit 6                    | 65 | Fig. XV-1  |        | <del>-</del>                                 | 101 |

| Fig. XII-2  | Gate for strobe amplifier               | 65 | Fig. XV-1  | -11 P  | rinted wiring board, horizontal              |     |

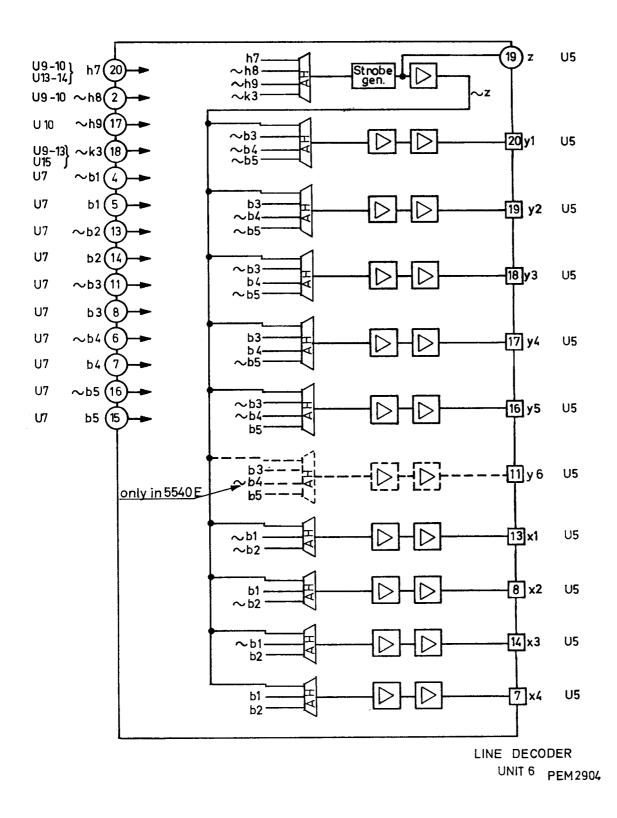

| Fig. XII-3  | Block-diagram, line decoder             | 66 |            | d      | lecoder -                                    | 103 |

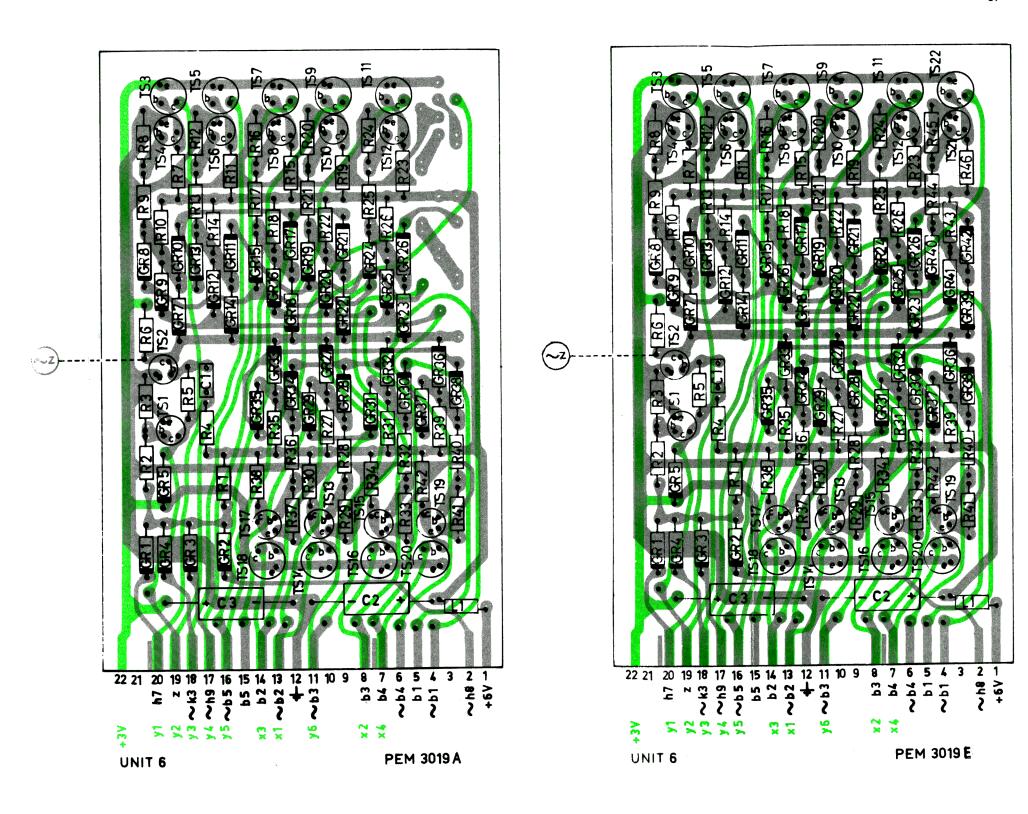

| Fig. XII-4a | Printed wiring board, line decoder      |    | Fig. XV-1  | 12 C   | Circuit diagram, horizontal decoder          | 105 |

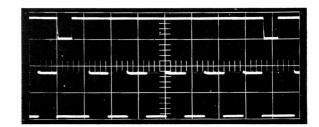

|             | (A version)                             | 67 | Fig. XVI-  |        |                                              | 108 |

| Fig. XII-4b | Printed wiring board, line decoder      |    | Fig. XVI-  | -2 P   | ulse diagram for "h2"                        | 110 |

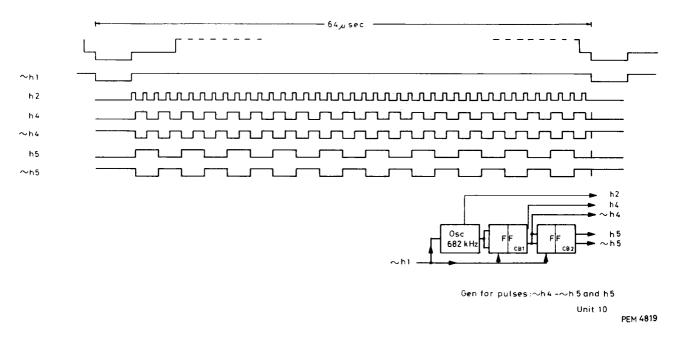

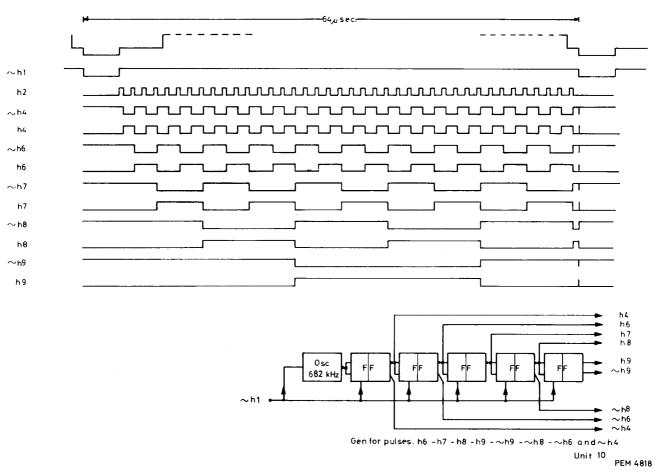

|             | (E version)                             | 68 | Fig. XVI-  | -3 P   | ulse diagrams for " $\sim$ h4", "h5" and     |     |

| Fig. XII-5  | Circuit diagram, line decoder           | 69 | -          |        | <del>-</del>                                 | 111 |

| Fig. XIII-1 | Pulse generator, pre-selector of line   | •  | Fig. XVI-  | -4 P   |                                              | 111 |

|             | register                                | 73 | Fig. XVI-  |        |                                              | 112 |

|             |                                         |    |            |        |                                              |     |

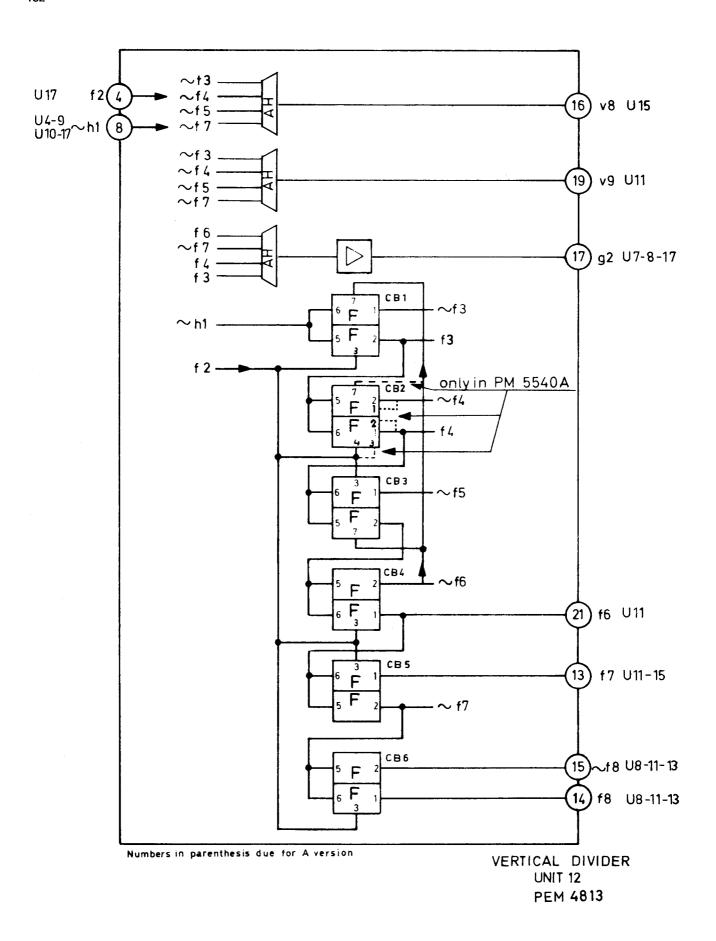

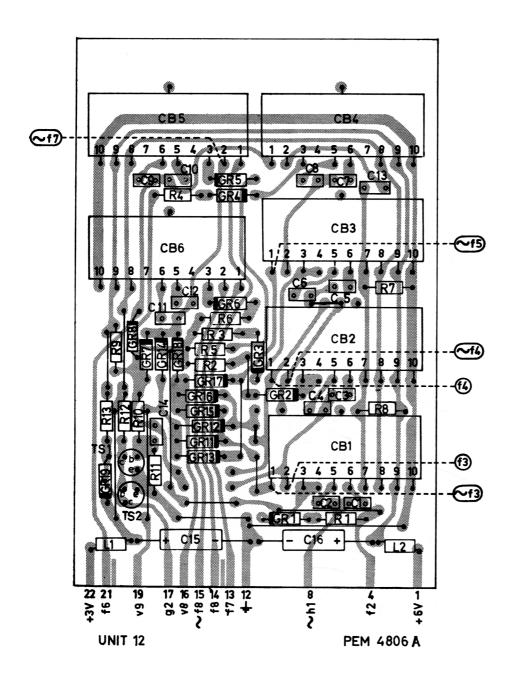

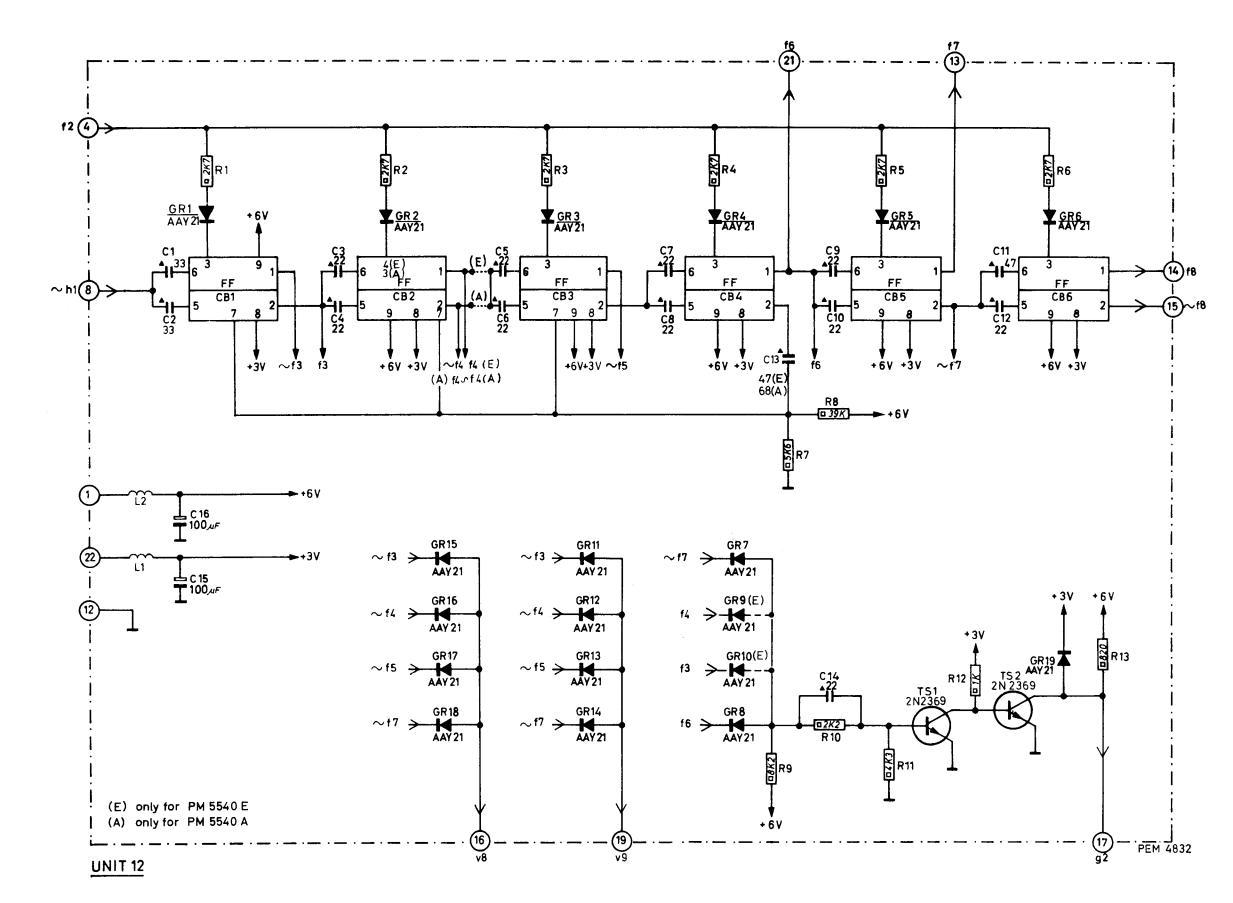

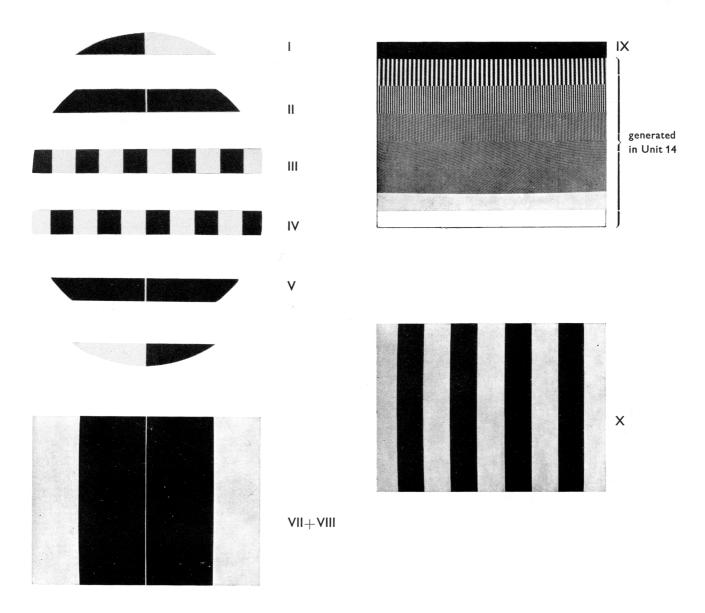

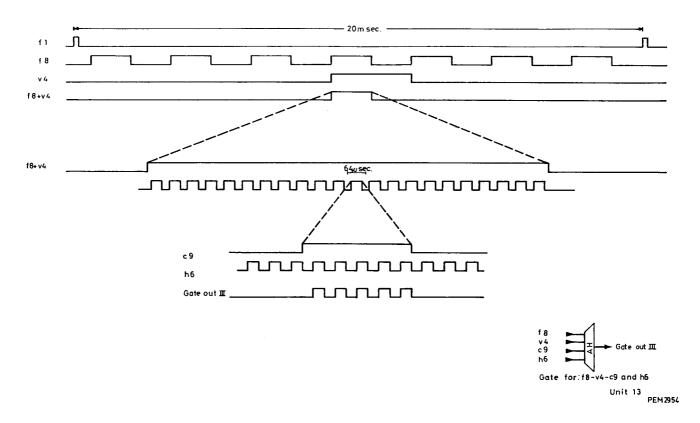

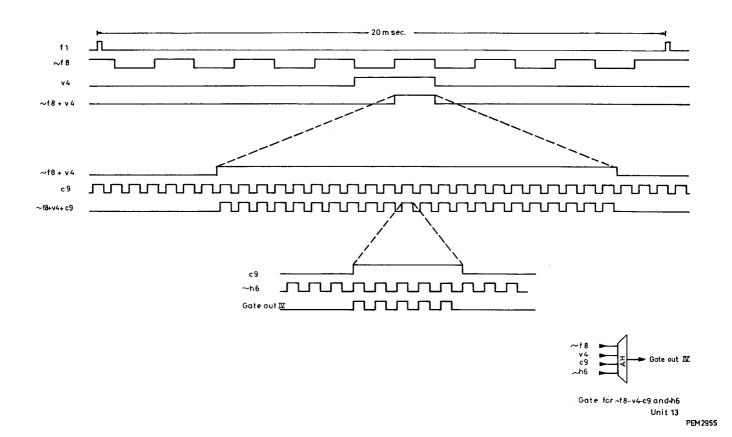

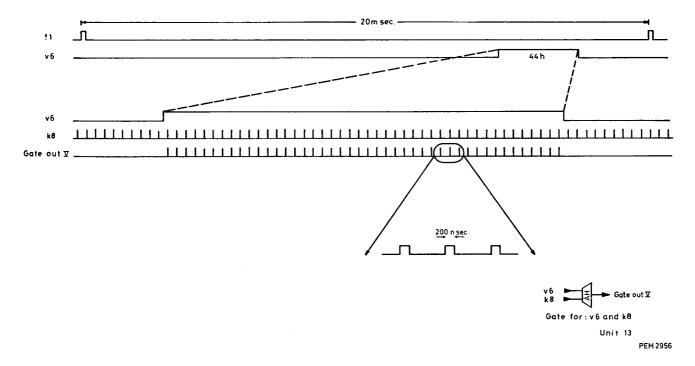

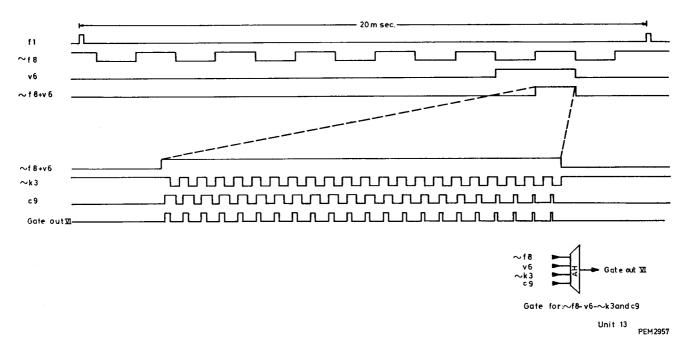

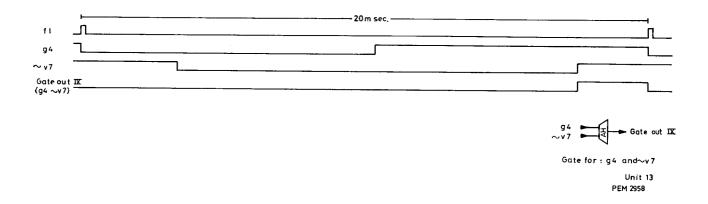

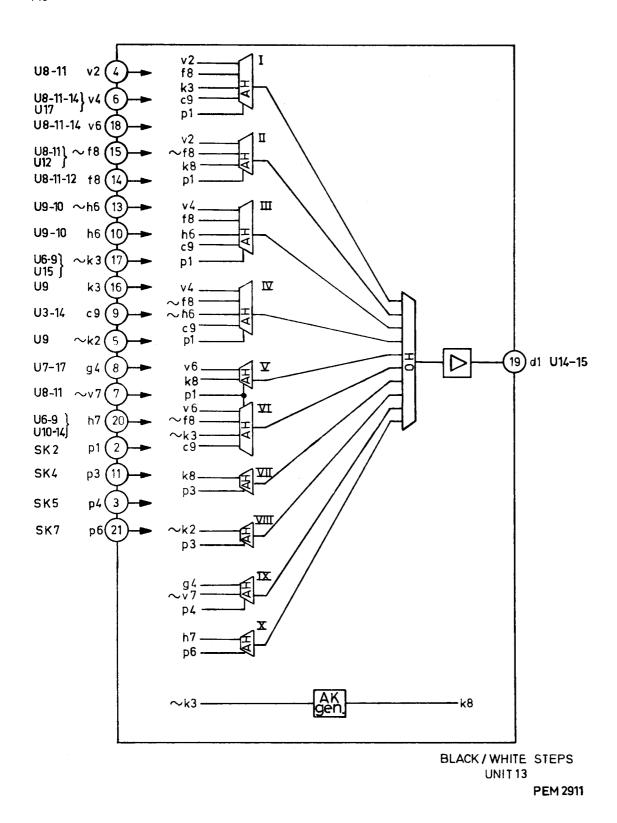

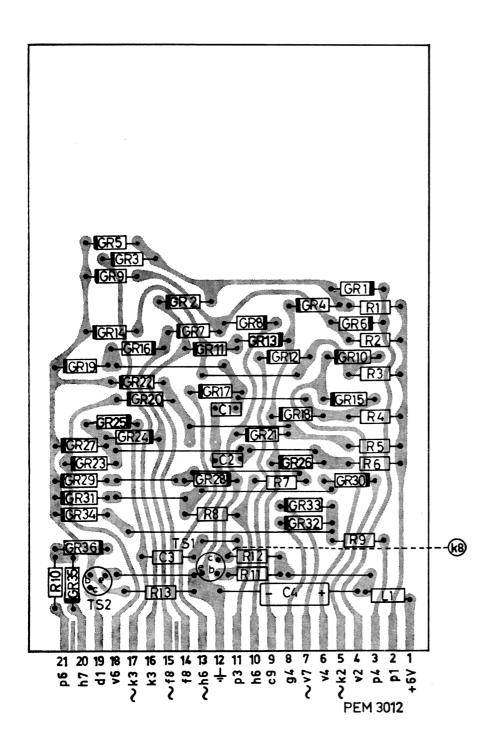

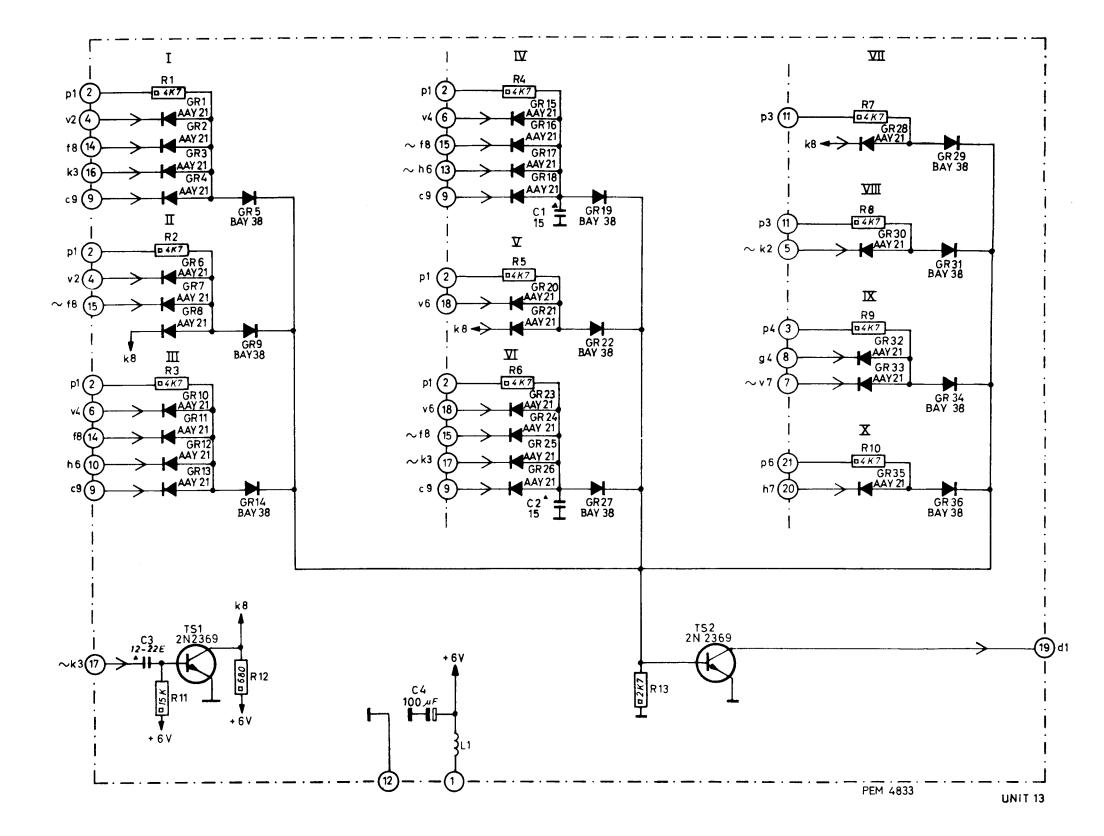

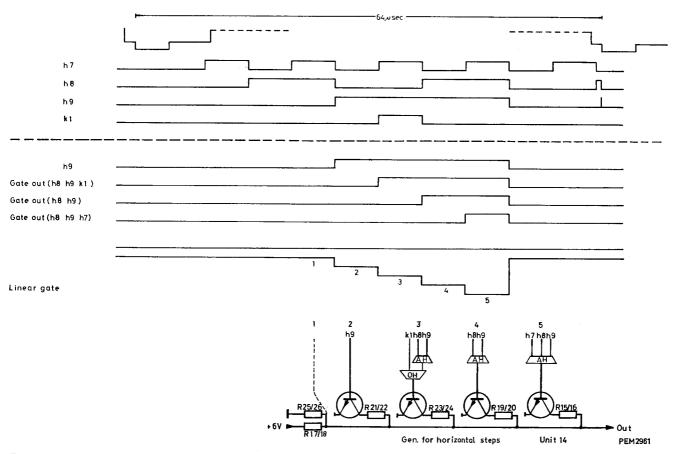

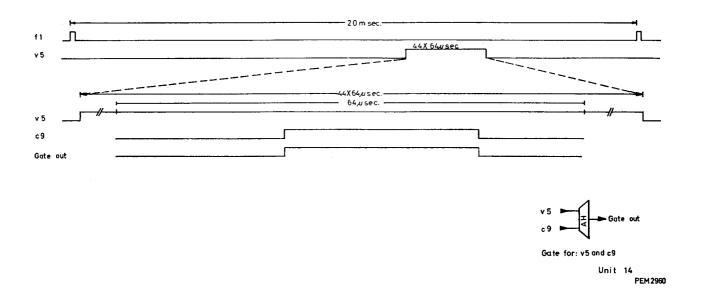

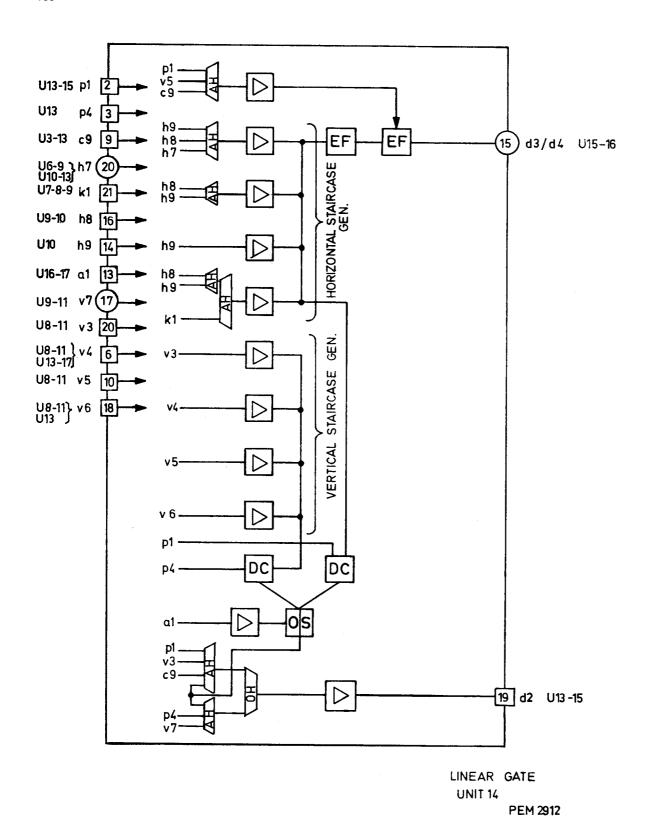

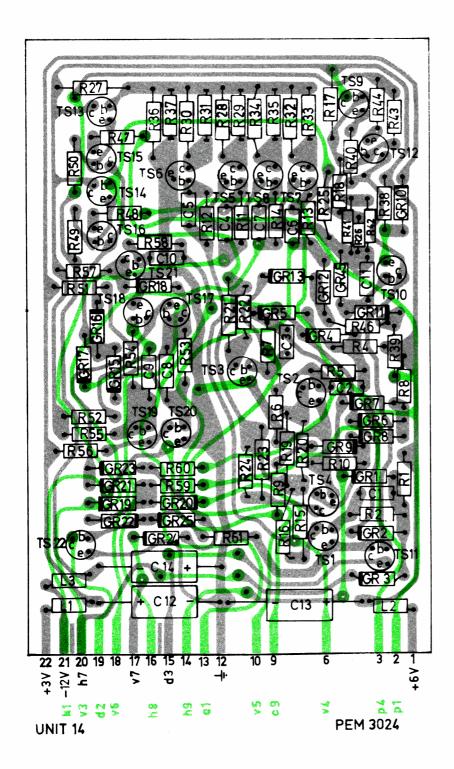

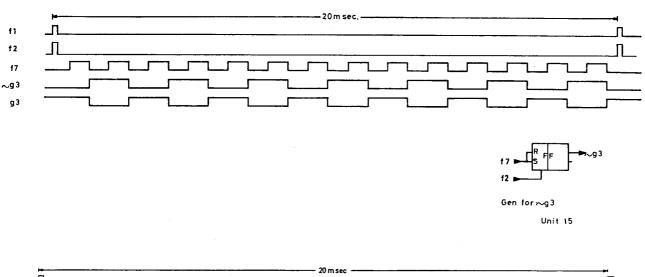

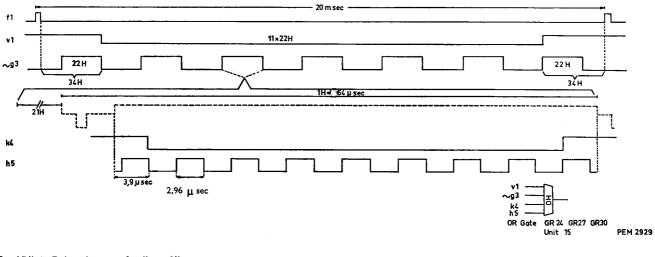

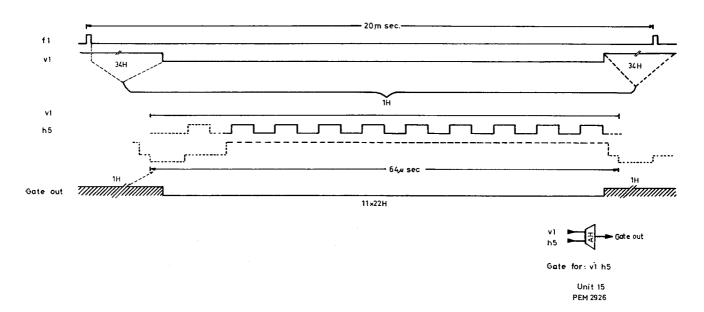

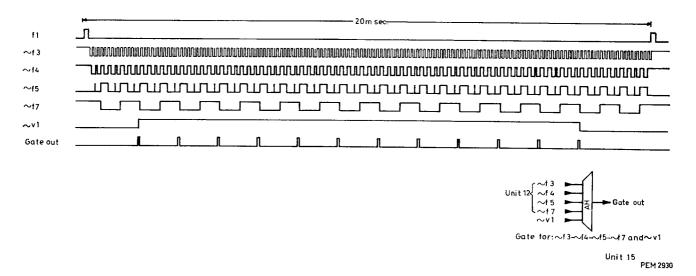

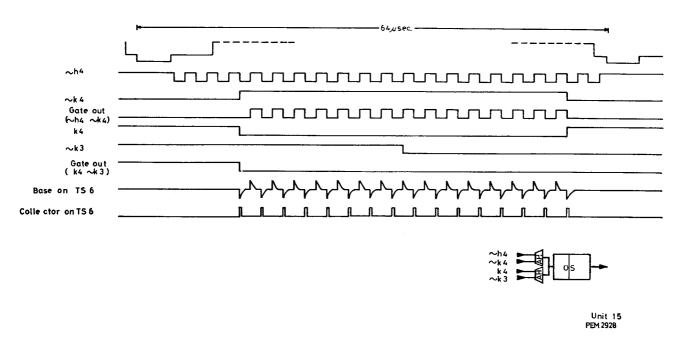

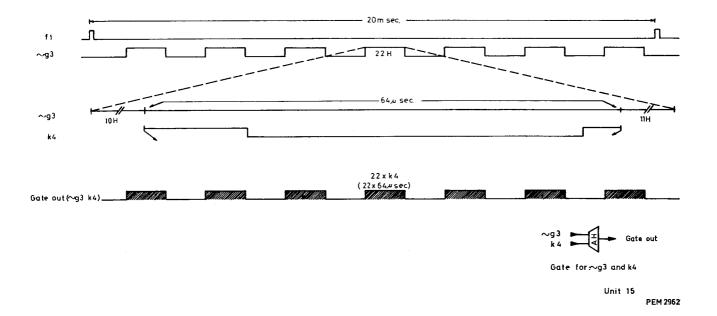

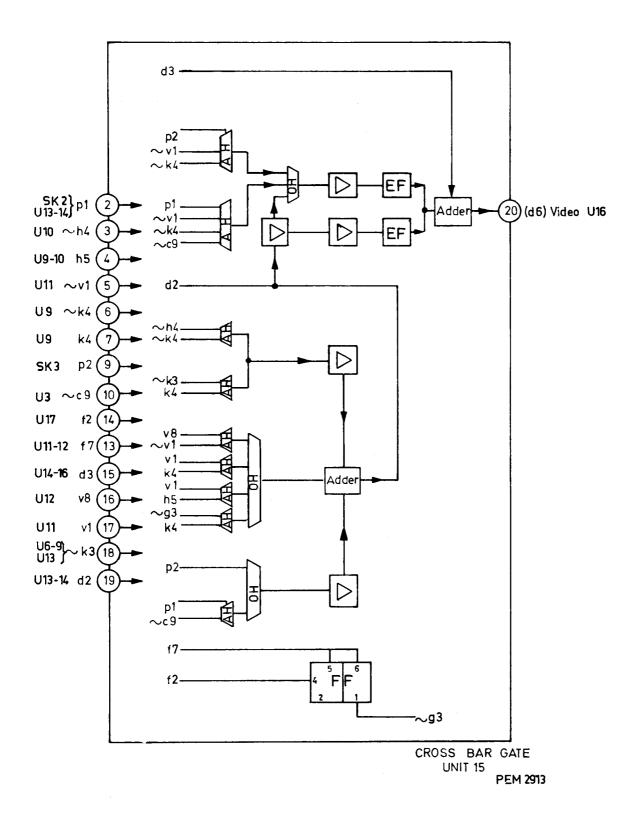

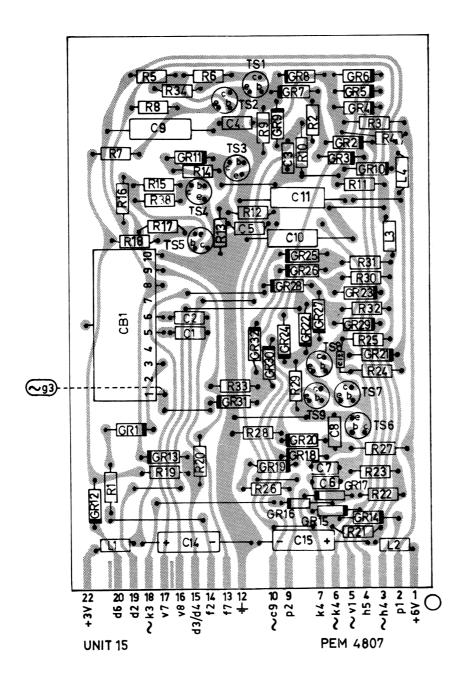

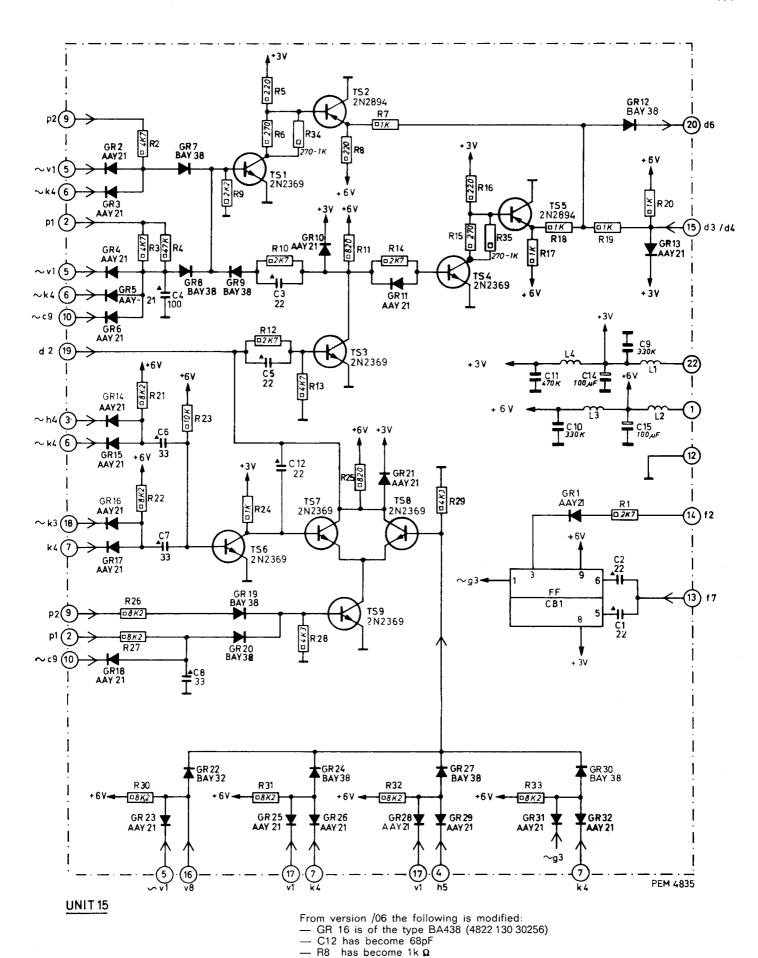

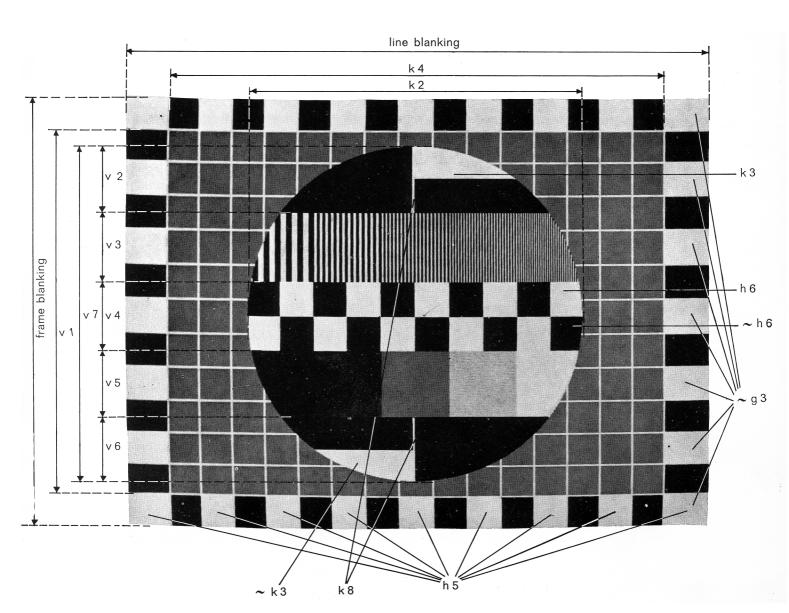

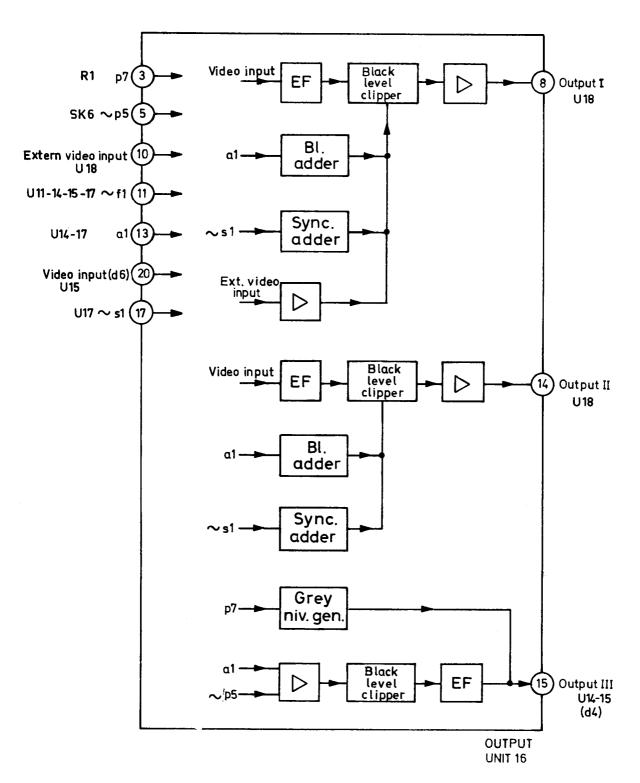

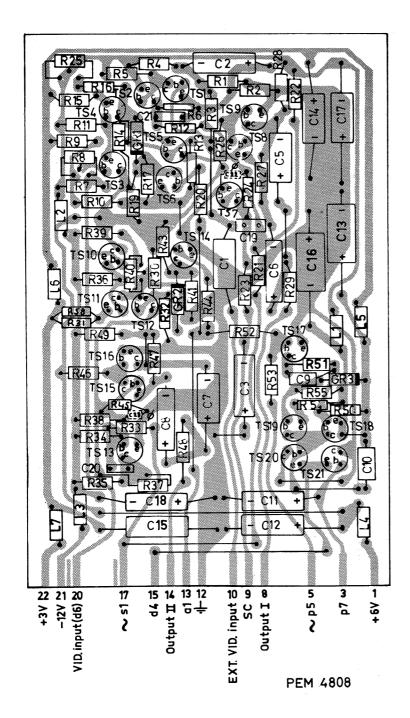

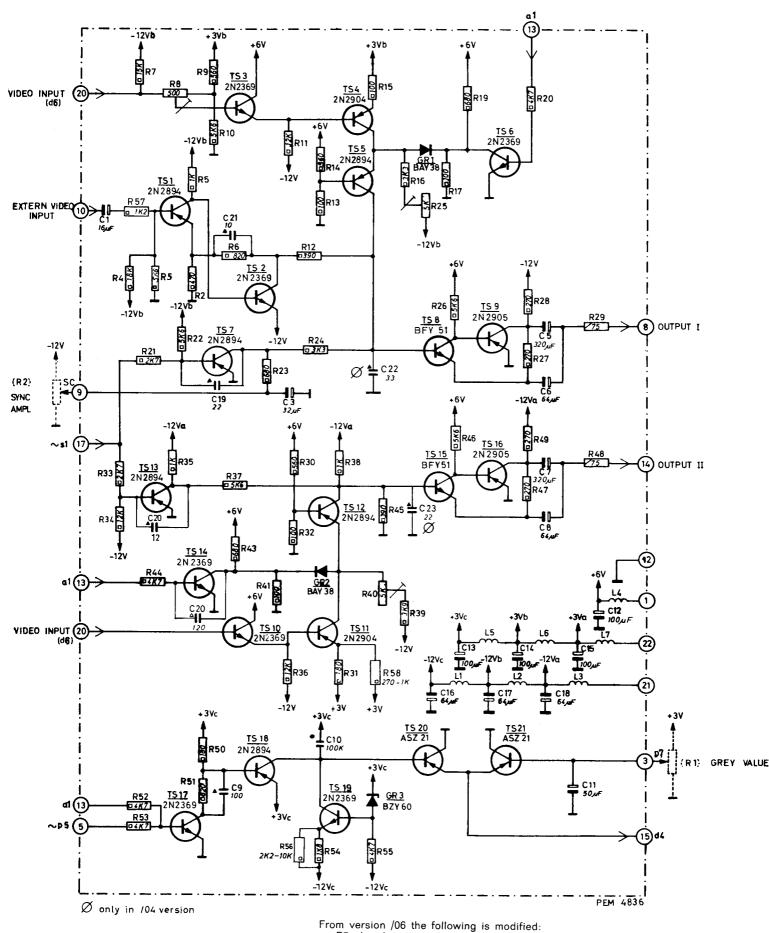

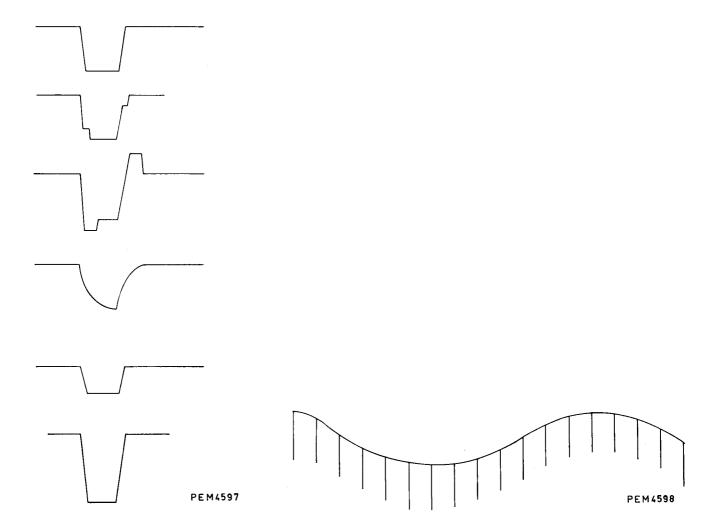

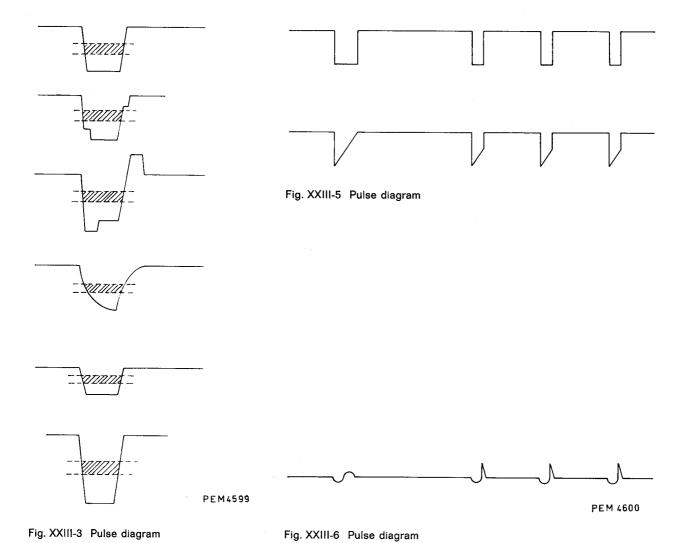

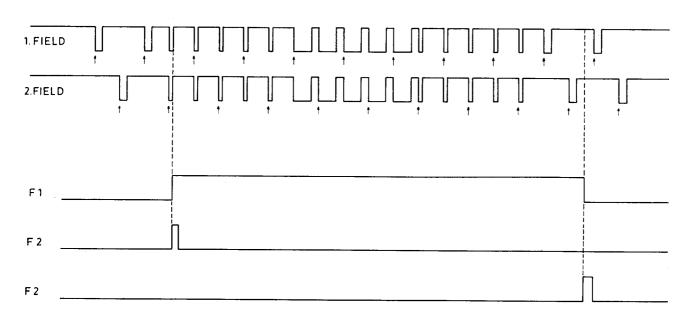

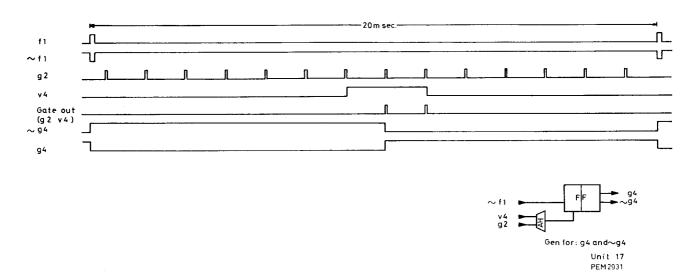

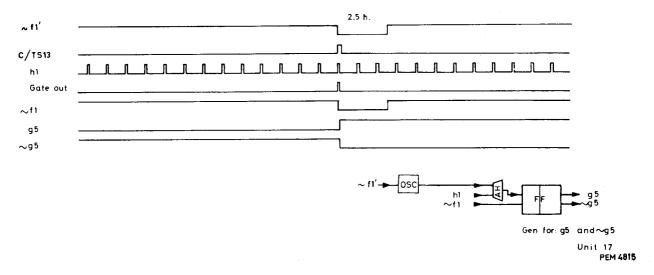

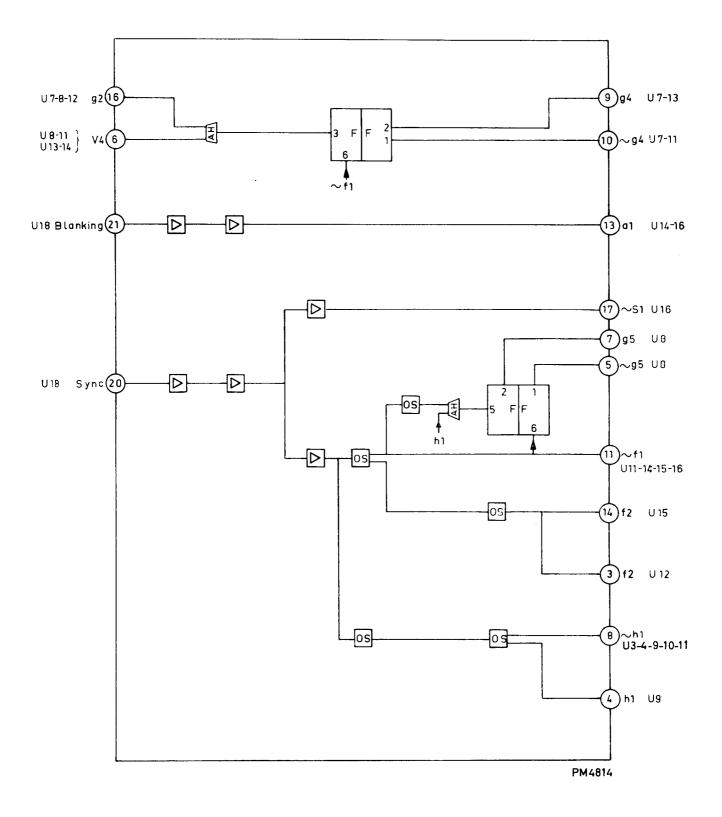

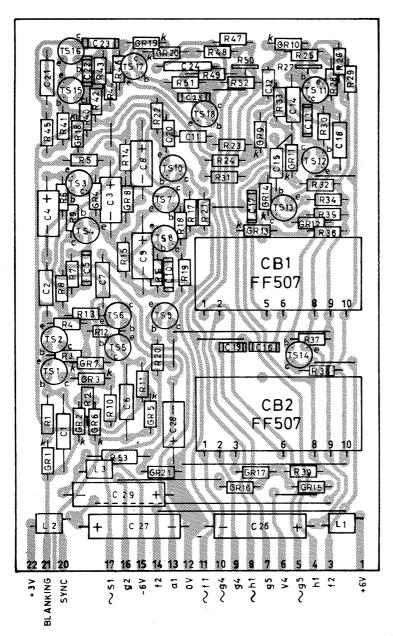

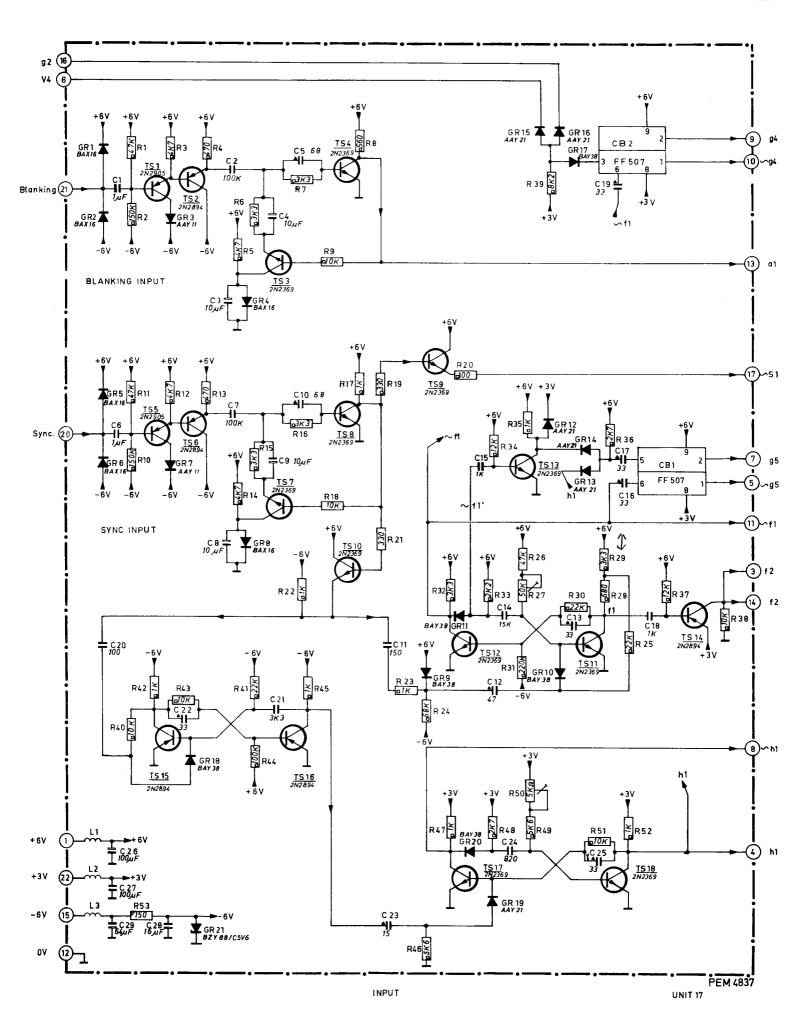

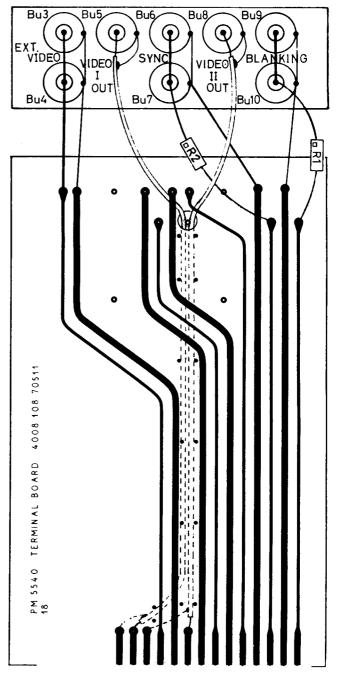

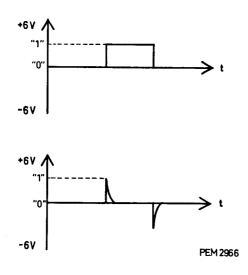

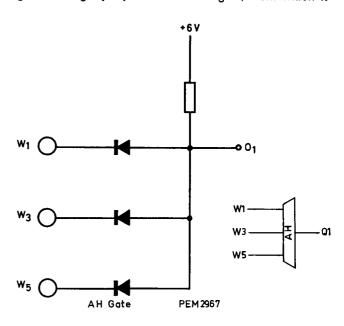

#### Fig. XVI-6 Printed wiring board, horizontal Fig. XX-5 Block-diagram, linear gate 158 divider Fig. XX-6 113 Printed wiring board, linear gate 159 Fig. XVI-7 Fig. XX-7 Circuit diagram, horizontal divider 115 Circuit diagram, linear gate 161 Fig. XVII-1 Oscillograms, Unit 11 118 Fig. XXI-1 Influence of "k4" and "v1" 165 Fig. XVII-2 Pulse diagrams for "v1" and "∼ v1" 120 Fig. XXI-2 Test pattern 165 Pulse diagrams for "v2" . . . "v6" Fig. XVII-3 120 Fig. XX1-3 Pulse diagrams for "k4" and "v1" 166 Pulse diagrams for "v7" and " $\sim$ v7" Pulse diagram for '' $\sim$ g3'' Fig. XVII-4 121 Fig. XXI-4 166 Fig. XVII-5 Block-diagram, vertical decoder 122 Fig. XXI-5 Pulse diagrams for "h5" and "v1" 167 Fig. XVII-6 Fig. XXI-6 Printed wiring board, vertical decoder 123 Pulse diagrams for " $\sim$ f3", " $\sim$ f4", Fig. XVII-7 Circuit diagram, vertical decoder " $\sim$ f5", " $\sim$ f7" and " $\sim$ v1" 125 167 Fig. XVIII-1 Oscillograms, Unit 12 129 Fig. XXI-7 Pulse diagrams for " $\sim$ h4", " $\sim$ k3", Fig. XVIII-2 Pulse diagrams for "f6", "f7", "f8" ''k4'' and '' $\sim$ k4'' 168 and $^{\prime\prime}\sim$ f8 $^{\prime\prime}$ 131 Fig. XXI-8 Pulse diagrams for " $\sim$ g3" and "k4" 168 Fig. XVIII-3 Pulse diagram for "g2" 131 Fig. XXI-9 Block-diagram, Cross-bar gate 169 Fig. XVIII-4 Block-diagram, vertical divider 132 Fig. XXI-10 Printed wiring board, Cross-bar gate 170 Fig. XVIII-5a Printed wiring board, vertical divider Fig. XXI-11 Circuit diagram, Cross-bar gate 171 (A version) 133 Fig. XXII-1 Test pattern 175 Fig. XXII-2 Fig. XVIII-5b Printed wiring board, vertical divider Block-diagram, video output 176 (E version) 135 Fig. XXII-3 Printed wiring board, video output 177 Fig. XVIII-6 Circuit diagram, vertical divider 137 Fig. XXII-4 Circuit diagram, video output 178 Fig. XIX-1 Parts of testpattern 141 Fig. XXIII-1 Pulse diagram of typical distortion 181 Fig. XIX-2 Oscillograms, Unit 13 141 Fig. XXIII-2 Pulse diagram of typical distortion 181 Fig. XIX-3 Pulse diagram of gate I 142 Fig. XXIII-3 Pulse diagram 182 Fig. XIX-4 Pulse diagram of gate II 142 Fig. XXIII-4 Pulse diagram for "f1" and "f2" 182 Fig. XIX-5 Pulse diagram of gate III 143 Fig. XXIII-5 Pulse diagram 182 Fig. XIX-6 Pulse diagram of gate IV 143 Fig. XXIII-6 Pulse diagram 182 Pulse diagram of gate V Fig. XXIII-7 Fig. XIX-7 144 Oscillograms, Unit 17 183 Fig. XIX-8 Pulse diagram of gate VI 144 Fig. XXIII-8 Pulse diagrams for ''g4'' and '' $\sim$ g4'' 185 Fig. XIX-9 Pulse diagram of gate IX 145 Fig. XXIII-9 Pulse diagrams for ''g5'' and '' $\sim$ g5'' 185 Fig. XIX-10 Block diagram, black/white steps 146 Fig. XXIII-10 Block-diagram, input amplifier 186 Fig. XIX-11 Printed wiring board, black/white Fig. XXIII-11 Printed wiring board, input amplifier 187 steps 147 Fig. XXIII-12 Circuit diagram, input amplifier 188 Fig. XIX-12 Circuit diagram, black/white steps 149 Fig. XXIV Printed wiring board, connection Fig. XX-1 Oscillograms, Unit 14 154 190 Fig. XX-2 Pulse diagrams for vertical steps 156 Fig. XXVI-1 Rear view of the instrument 199 Fig. XX-3 Pulse diagrams for horizontal steps 156 Fig. XXVI-2 Front view of the instrument 200 Fig. XX-4 Pulse diagrams for "v5" and "c9" 157 Fig. XXVIII-1 Front view of the instrument 202 Fig. XXVIII-2 Rear view of the instrument 203

## **I** Introduction

#### **GENERAL INFORMATION**

The PHILIPS PM 5540 is an extremely stable professional source of electronic test patterns.

It has been designed for use when developing and manufacturing television receivers, in television labor-

atories, in television studios and in television broadcasting stations.

The synchronizing and blanking signals are obtained from a PHILIPS TV-pulse generator PM 5530.

### II Technical data

Properties expressed in numerical values with tolerances stated, are guaranteed by us. Numerical values without tolerances stated, represent the properties of an average instrument and merely serve as a guide.

A PM 5540E (CCIR-version) can be converted to a PM 5540A (RTMA-version) by modifying four units (memory, line decoder, line register and vertical divider).

#### 1. Inputs

Sync. and blanking External video

Input impedance

#### 2. Outputs

Video output I

Video output II Output impedance Set-up

#### 3. Rise time-pulse width etc.

Rise and decay time of video transitions

Pulse width of vertical lines and needle pulse

Width of horizontal lines

Definition lines

#### 4. Linearity

Grey scale staircase

Line sawtooth

#### 5. Power supply

Voltage

Amplitude: 2-8 V<sub>pp</sub> negative

Amplitude: 0.7  $V_{\rm pp}$ , exclusive sync. External synchronized video information is added linearly to the signal present on ''OUTPUT I''.

. High

Nominal output 1  $V_{pp}$  inclusive sync.

Sync. ampl. is adjustable approx. 0-200 % by screw-driver control on front panel ("SYNC.AMPL.")

Video signal (excl.sync.) can internally be adjusted from 0.5  $V_{\rm pp}$  to 1  $V_{\rm pp}$ .

Amplitude 1 V<sub>pp</sub>, inclusive sync.

75 Ω

no set-up; can be added (see checking and adjusting unit 16).

< 100 nsec.

200 nsec.  $\pm$  20 nsec. (T 50 %) 2 picture lines, one in each field.

Square waves having frequencies of 0.8-1.8-2.8-3.8-4.8 MHz  $\pm$  2%, fixed phase relation. Rise time approx. 50 ns.

5 equal steps, amplitude of each step within  $\pm$  10 % of each nominal value.

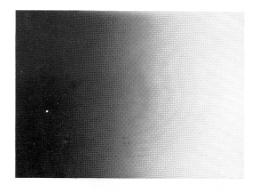

Direction black-white, full video amplitude.

115/230 V  $\,\pm\,$  20 % to be selected by a 2 position switch.

Mains frequency Consumption Fuse

6. Temperature range

7. Mechanical specification

**8. Versions** PM 5540A PM 5540E

50-60 Hz 40 W at 220 V.

For 90-160 V: 500 mA, delayed action For 180-320 V: 250 mA, delayed action

Operating conditions  $-10^{\circ}$  to  $+45^{\circ}$  C.

Width: 19".

Height: 3 units = 150 mm, incl. feet Depth: 420 mm, including handles.

Weight: 11.5 kg.

The instrument is delivered as a table model, but can

be easily converted into a 19" rack model.

for RTMA - 525 lines system for CCIR - 625 lines system

## **III Accessories**

With the instrument are delivered 1 operating- and service manual 1 mains cable 7 BNC connectors 5 BNC connectors with 75Ω load.

## IV Description of simplified block diagram

#### 1. Input amplifier

The instrument has to be driven with 2 signals ("SYNC"-"BLANKING"), available from e.g. a PHILIPS TV pulse-generator PM 5530. It has a high input impedance and contains circuits which make the performance independent of the amplitude of the input pulses.

#### 2. Vertical divider and decoder

This section generates all the gating signals on a field frequency basis. The signals are decoded to give the horizontal lines as well as the intervals in vertical direction.

#### 3. Horizontal divider and decoder

The line gating signals are derived from an oscillator, controlled by the line pulses. The signals are decoded to give the gating pulses in the horizontal direction.

#### 4. Circle generator

The circuitry used is based on digital techniques. The gating signals are obtained from a counting register, being operated from a clock-frequency oscillator.

The register is set for each line from a non-destructive ferrite-core-memory. The information is read-out from the memory line after line, selected by the line register. The electronic circle is completely locked to the rest of the pattern.

#### 5. Cross-bar generator

This section generates the grey background, the horizontal and vertical white lines as well as the black-white squares at the borders.

#### 6. Gradation

The 5 gradation steps are obtained by adding together suitable output signals of the horizontal divider.

#### 7. Saw-tooth information

The saw tooth is made by charging a capacitor with a constant current generator.

#### 8. Black-white steps and vertical bars

These signals are obtained by adding together suitable output signals of the horizontal divider.

#### 9. Definition lines

The definition lines are generated by a square-wave oscillator controlled by a vertical or a horizontal step signal.

#### 10. Adder circuit

The signals from the pattern generators are added together in a resistive matrix.

#### 11. Output amplifier

The two amplifiers have 75  $\Omega$  output impedance and supply the complete video signal including sync. Furthermore through one of the amplifiers a synchronized external video signal can be added to the electronic test-pattern.

### **V** Installation

#### **OPERATING INSTRUCTIONS**

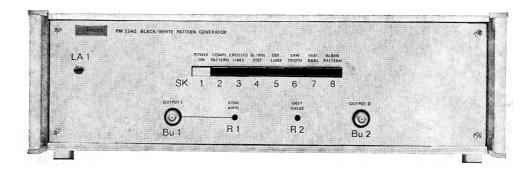

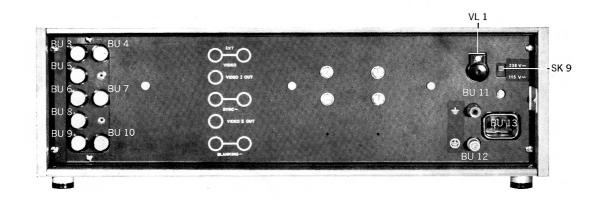

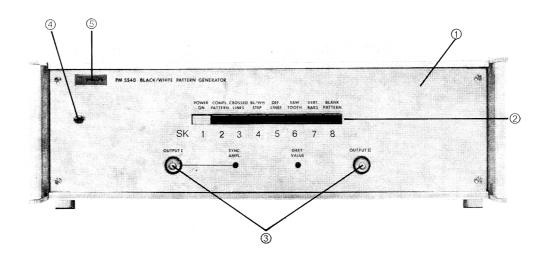

Fig. V-1 Front view of the instrument

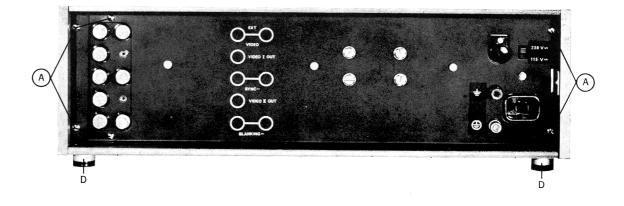

#### A. Adjusting to the local mains voltage

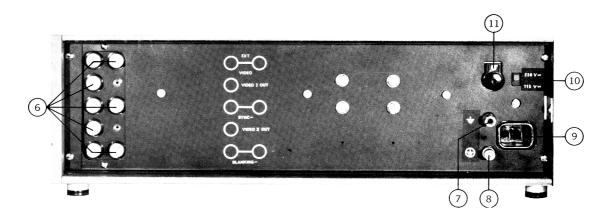

By means of the voltage selector SK9 the instrument can be adjusted to mains voltages of 115 V or 230 V,  $\pm$  20 % (50-60 Hz).

The selected value can be read near the switch.

The instrument can be adjusted to the other mains voltage as follows:

- loosen screw "A" (Fig. V-2):

- set the switch to the desired voltage range:

- fasten screw "A" again:

- replace fuse VL1:for 115 V = 500 mA (delayed-action type)

for 230 V - 250 mA (delayed-action type)

#### B. Earthing

Earth the instrument in accordance with the local safety regulations.

The metal cabinet can be earthed via:

socket BU12 (see Fig. V-2) and the earthing core of the mains lead.

The electrical circuit can be earthed via:

socket BU11 (see Fig. V-2) and the screening of the coaxial connection cables.

Avoid double earthing of the electrical circuit, because this may introduce hum phenomena.

#### C. Mounting in a 19" rack

- Remove the four screws "B" (Fig. V-2).

- Remove the four feet "C" (Fig. V-2) by turning them anti-clockwise.

- Screw the feet into the threaded holes (of screws "B") in the rear-panel.

Fig. V-2 Rear view of the instrument

- Remove the screws "D" (Fig. V-3) and pull the brackets "E" out.

- Insert the bracket "E" as shown in Fig. V-4.

- The instrument can now be mounted in a 19" rack with screws inserted through the holes "F" in the brackets.

Fig. V-3 Side view

Fig. V-4 Side view

## VI Survey of controls and sockets

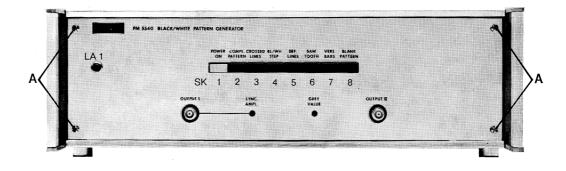

Fig. VI-1 Front view of the instrument

#### A. Front of the instrument

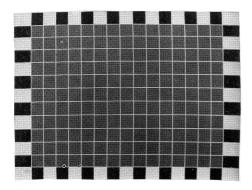

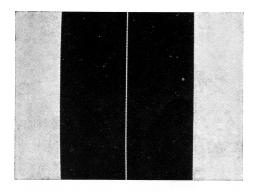

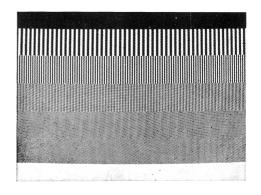

Test patterns at "VIDEO I OUT" and "VIDEO II OUT" by depressing push-button:

SK1 "POWER ON"

Mains switch

SK2 "COMPL. PATTERN"

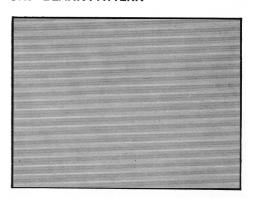

SK3 "CROSSED LINES"

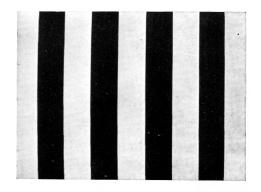

SK4 "BL/WH STEP"

SK5 "DEF. LINES"

SK6 "SAW TOOTH"

SK7 "VERT. BARS"

SK8 "BLANK PATTERN"

#### R1 "SYNC. AMPL."

For varying the amplitude of the sync. pulses of the pattern at "OUTPUT I" between 0 and 200 %

#### **R2 "GREY VALUE"**

To vary the grey value of the "BLANK PATTERN"-signal

#### **BU1** "OUTPUT I"

Output socket for the selected test pattern.

Amplitude: 1  $V_{p-p}$  inclusive sync.

Sync. ampl. adjustable 0-200 % (see description of R1)

#### B. Rear of the instrument

#### BU3 and BU4 "EXT. VIDEO"

Input socket for a synchronized external video signal; This signal will be added linearly to the internal signal on BU1 "OUTPUT I".

Amplitude: 0.7  $V_{p-p}$  (excl. sync.)

Polarity: White positive-sync. negative

Input impedance: High (The signal can be looped

through)

#### **BU5 "VIDEO I OUT"**

Output socket for the selected test pattern Interconnected with BU1 "OUTPUT I" (front)

Fig. VI-2 Rear view of the instrument

Vision ampl. internally adjustable 0.7-1.4  $V_{\rm p-p}$ . Polarity: White positive-sync. negative

Output impedance:  $75\Omega$

Interconnected with BU5: "VIDEO I OUT" (rear) (See also description of BU3: "EXT. VIDEO")

#### **BU2** "OUTPUT II"

Output socket for the selected test pattern

Amplitude: 1  $V_{p-p}$  inclusive sync.

Polarity: White positive - sync. negative

Output impedance: 75  $\Omega$

Interconnected with BU8: "VIDEO II OUT" (rear)

Separated from BU1: "OUTPUT I".

#### BU6 and BU7 "SYNC."

Input socket for the complete synchronizing signal

Amplitude: 2-8 V<sub>p-p</sub> Polarity: negative Input-impedance: high

#### **BU8 "VIDEO II OUT"**

Output socket for the selected test pattern Interconnected with BU2 "OUTPUT II" (front)

#### BU9 and BU10 "BLANKING"

Input socket for the blanking signals

$\label{eq:amplitude: 2-8 Vpp} Amplitude: 2-8 \, V_{p\cdot p} \\ Polarity: negative \\ Input-impedance: high \\$

#### BU11 " + "

Earth terminal: connected to the common of the circuits of the instrument

#### BU12 " 😩 "

Earth terminal: connected to the cabinet of the instrument

#### **BU13**

Mains socket

Sk9 "115 V $\sim$  – 230 V $\sim$ "

Mains voltage selector

#### VL1

Fuse for 115 V mains, 500 mA, delayd-action for 230 V mains, 250 mA, delayd-action

#### C. Changing testpatterns

To fulfil special demands of users, the display of some testpatterns can be altered slightly.

However, one should bear in mind that return to the original situation is not easy because the alternations are made by modifying some of the internal circuits.

- a. Removing the black/white squares, surrounding the test patterns "COMPL. PATTERN" AND "CROSS-ED LINES".

- From Unit 15 ("CROSSBAR GATE") remove diodes GR2-3-4-5-15-16-17-23-24-27 and 30.

- b. Removing the lowest needle pulse (inside the circle) from test pattern "COMPL. PATTERN".

From Unit 13 ("BLACK/WHITE STEPS") remove diodes GR20 and 21.

#### D. Connections

Apply the following signals to the indicated sockets at the rear:

- Complete sync. signal to socket "SYNC.-"

- Complete blanking signal to socket "BLANKING-"

These signals can be taken from the PHILIPS TV-pulse generator PM 5530.

If desired, connect a synchronized video signal to "EXT, VIDEO"

#### NOTE:

When sockets BU4, BU7 and BU10 are not used for linking-through purposes, they should be terminated with the supplied 75  $\Omega$ -loads. Sockets "VIDEO I OUT" and "VIDEO II OUT" on the rear are connected in parallel to sockets "OUTPUT I" and "OUTPUT II" resp. on the front. The output impedance is already 75  $\Omega$ , so they should not be terminated when they are not used.

## VII The principle of the circle generator

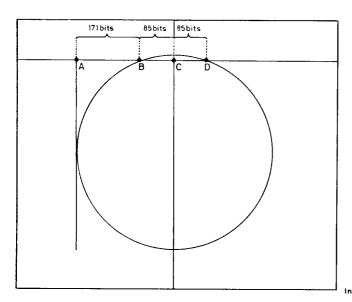

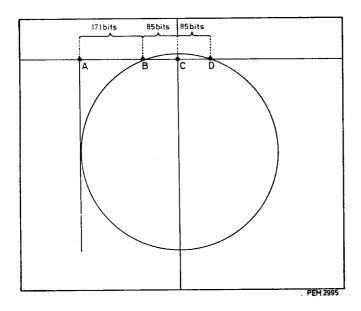

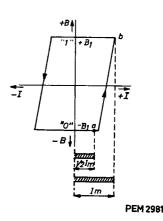

The circle on the TV screen is built up of a number of line-segments BCD (Fig. VII-1). For each line of the pattern the length of BCD has a very definite value, determined by the size of the circle.

The size of the circle in proportion to the entire TV pattern is expressed in quantities of time, (the time it takes to scan the line segments AB, BD respectively). This time has been converted into a binary figure that is characteristic for each single line. The conversion of the binary figure into time is made in an electronic counter or register, which counts a number of pulses from a clock-pulse oscillator. For each line the circle register counts the number of pulses corresponding to the distance AB.

In this way the semicircle B is converted into a number of figures, each line having its typical binary figure, corresponding to the distance AB.

These figures are stored in a magnetic-core memory from which they are transferred to the circle register for each line. The right semicircle D is made as an image of the left semicircle, as BC = CD.

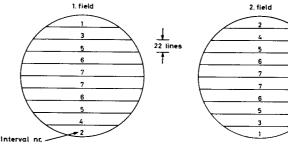

In each field the circle will contain 220 lines.

The lengths of the line-segments AB, BC and CD correspond to a whole number of clock-pulses, the frequency of which (approx. 17 MHz) is high enough to produce a sufficiently smooth circle. At a lower frequency the circle would be serrated.

Fig. VII-1 Principle of the circle generator

Fig. VII-2 Intervals of the two fields

The time it takes to scan the line ABC will be 15  $\mu$ s., while the number of clock pulses (bits) covering this time should be a "round" binary figure, i.e. 2, 4, 8, 16, 32, 64, 128, 256 or 512.

In practice 256 bits will meet the requirements, which results in a frequency of approx. 17 MHz.

#### A. The Circle register

The memory contains information about the distance AB for each line. This information is stored in binary form

Fig. VII-1 shows, for example, a line, for which the distance AB is equal to 171 clock pulses (bits), and the distance BC to 256 - 171 = 85 bits.

The figure 171 is in binary form = 10101011, and at the beginning of the line in question, this figure is read out of the memory and put into the circle register, which will thus be set for this figure.

At point A the 17 MHz oscillator is started, and the register begins to count. The register is connected so that it counts down from the set figure 10101011 to zero.

Passing zero the register delivers a pulse to the flipflop oscillator which determines point B on the circle; thereby the distance AB will correspond exactly to 171 pulses The register continues counting, until the centre line of the circle is reached (in this example it has counted 85 bits). At the centre line C an external pulse is supplied to the register, which makes it change over to counting in the opposite direction.

After having counted again 85 pulses, zero is reached once more, and a pulse triggers again the flip-flop oscillator, which determines the point D on the circle. Therefore the distance CD will be the same as the distance BC on the circle.

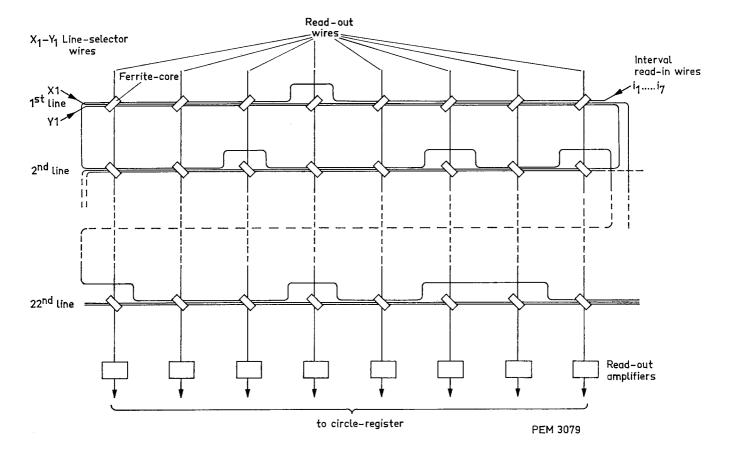

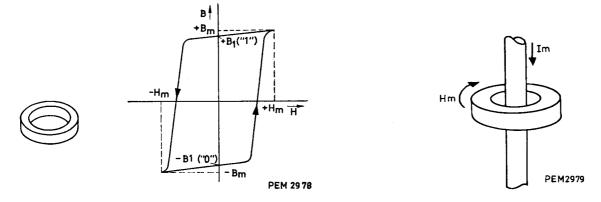

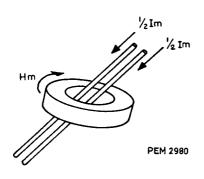

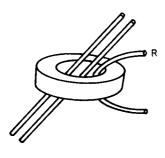

#### B. The Memory

The amount of information to be stored in the memory is so large that a ferrite core is the obvious solution.

For each line the counter of the circle register is actuated, so that it forms the correct binary figure. For a circle with 220 lines it should be done by means of a rectangular matrix with 220 inputs and 8 outputs, this means a matrix with  $8 \times 220 = 1760$  cores.

However, the size of the memory has been reduced considerably by dividing the circle in groups of lines (intervals), each containing 22 lines, as will be described later on. The size of the memory will, therefore, only be  $22 \times 8 = 176$  cores.

The one wanted of a 22 line-group is selected during the read-out time, and the read-in is effected by means of different read-in wires, one for each interval. So the real memory function has been placed in the wiring of the read-in wires. Each wire passes some cores, and bypasses others, depending on the value

of the binary figure. Consequently, the threading of the interval wires through the cores is rather complicated.

As soon as the interval wires have distributed the information over the 22 binary figures as magnetism in the cores selected, the figures are read-out line after line.

When the read-out of the 22nd line is finished, the interval wires for the next interval will place another 22 binary figures in the memory, and then these figures are read-out and transferred to the register, etc.

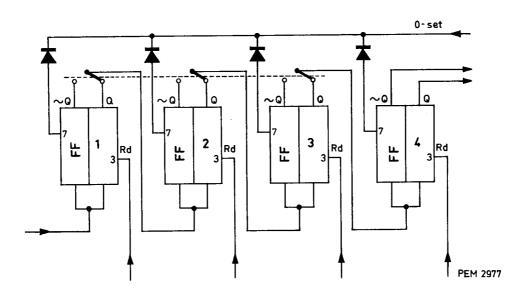

#### C. Line-selector register

As mentioned, the memory is sensed line after line through the successive 22 lines. For this process 22 sensing wires and 22 continuous sensing pulses would be necessary. The 22 pulses could be obtained from a shift register of 22 positions and triggered by line pulses.

Instead of this a binary divider (line-selector register) is used, followed by a decoder unit (line-selector decoder). Each binary figure will be decoded and delivers control signals for each single line.

This simplification of the "decoder matrix" is made by placing part of the decoding in the threading of the memory. Instead of decoding down to 22 pulses, the decoder delivers  $4 \times 6$  pairs of pulses on only 10 sensing wires. (X- and Y-wires). Each sensing line actually consists of 2 wires connected in parallel. Only when the pulses of the two wires are in phase, the current will be strong enough to magnetize the cores and to produce an output signal for the counting register. Out of 24 (4  $\times$  6) combination for the CCIR system only 22 will be used. For the RTMA system 20 are used and for the French system all 24.

#### D. Interval selector

The circle is built up of 220 lines in each field, and these lines are divided into 10 groups of intervals, each containing 22 lines. For a complete frame of two consecutive fields 20 intervals will be needed in total. However, not all intervals are different. The interlacing, which in principe makes the two fields different, has no influence on the central part of the circle, so the 6 intervals, numbered 5, 6, 7 in Fig. VII-2, in the middle of the circle can be used for both fields. The two intervals at the top of the first field can be considered an image of the corresponding intervals at the bottom of the second field. Consequently, only 4 intervals are needed for this part of the circle, and the whole circle can be built up of 4 + 3 = 7 intervals. The placing of these intervals in the circle is shown in Fig. VII-2. To select the right interval for the right place in the circle, the interval selector is used. It consists of a number of gates and is supplied with pulses, which, according to certain combinations, will deliver magnetizing forces in the correct succession.

## VIII Description of detailed block-diagram

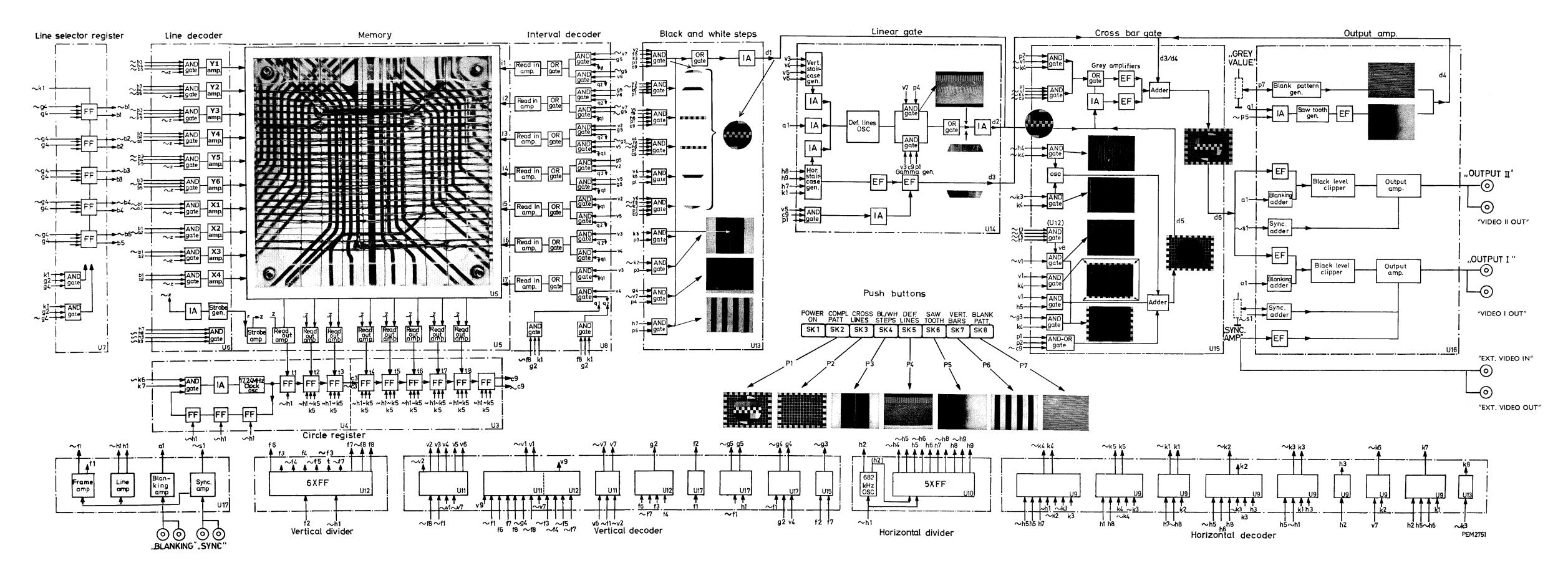

The block-diagram is composed of 4 main groups:

- Input amplifiers

- Pulse generators (to control and drive the pattern generators)

- Pattern generators

- Output amplifiers.

#### Note:

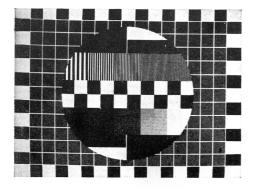

In this block-diagram the pictures at the connections between units 13, 14, 15, and 16 are the ones present when button "COMPL. PATTERN" is depressed. Other signals will be present when one of the other push-buttons is depressed.

#### A. Input Amplifiers (part of U17)

The amplifiers have an high input impedance so that the input signals can be looped through without reflections.

#### B. Pulse Generators

They can be subdivided into 3 sections:

- Vertical divider and decoder

- Horizontal divider and decoder

- Generator for the circle-pulse.

#### 1. Vertical Divider and Decoder

This section generates all the gating signals on a frame basis. The signals are obtained by counting down the line pulses ( $\sim$  h1) in a 6-stage divider. The output signals from this divider are decoded to give the horizontal lines as well as the 8 intervals in vertical direction.

#### 2. Horizontal Divider and Decoder

The line gating signals are derived from a 682 kHz oscillator, controlled by the line pulses. This oscillator signal is counted down in a 5-stage binary counter, the output signals of which are decoded to give the gating pulses in the horizontal direction.

#### 3. Generator for the Circle pulse

The circle generator supplies 2 signals, "c9" and " $\sim$  c9", which are in anti-phase. The positive one,

"c9", is used to emphasize the circle-area with the composite pattern, while the negative one, " $\sim$  c9", blanks the circle-area to make room for the composite circular pattern. The "c9"-pulses are obtained from a counting register that will count-down or forward the pulses from a 17.24 MHz clock-pulse oscillator. (Units 3 and 4)

The register is set for each line by pulses from a non-destructive ferrite core memory via 8 read-out amplifiers. The clock-pulse oscillator is started by " $\sim$  k6"-pulses and stopped by "k7"-pulses.

To ensure that the oscillator stops after a complete number of periods, the clock-pulse is fed back, via 3 flip-flops, to the and-gate, thus establishing a phase-lock

By simultaneously supplying some cores with an X-and an Y-current (e.g.  $X_1 + Y_2$ ) from the line decoder (unit 6), the memory is sensed line after line. The line decoder is controlled by the line-selector register (unit 7) that counts the "k1"-pulses, which are repeated in the middle of each line. The sensing moment of the cores is determined by the " $\sim$  z"-pulses originating from the strobe generator.

The memory consists of  $22 \times 8$  cores and can, therefore, only contain information about 22 lines at the same time. As a result of this, after 22 lines (= one interval) the memory will receive new information about the next 22 lines from the interval decoder. This continues until all the 7 intervals, necessary to compose the circle, have been read-out. The interval decoder is controlled by pulses from the vertical and horizontal dividers and decoders.

#### C. Pattern Generators

They can be subdivided into 4 sections:

- Black and white steps

- Linear gate

- Cross-bar gate

- Blank pattern and sawtooth signal

#### 1. Black and White Steps

When push-button "COMPL. PATTERN" is depressed, the first 6 and-gates (from the top) are producing parts of the circular pattern as shown in the block-diagram. As these gates are also controlled by the circle pulse (c9), they produce a pattern inside the circle-area only.

When push-button "BL/WH STEPS" is depressed, the 8th and-gate delivers the wide black bar on a blank pattern, while the 7th and-gate produces the thin white line in the middle of the black bar.

When push-button "DEF. LINES" is de pressed, the 9th and-gate produces a black picture with one horizontal white bar at the bottom for the definition lines test pattern.

When push-button "VERT. BARS" is depressed, the 10th and-gate produces a black picture with vertical white bars.

#### 2. Linear Gate (Unit 14)

The generators deliver a horizontal and a vertical staircase signal, respectively.

When push-button "DEF. LINES" is depressed, the vertical staircase signal controls the definition lines oscillator to obtain a pattern containing 5 horizontal bars with definition lines.

When push-button "COMPL. PATTERN" is depressed, the horizontal staircase signal controls the definition-lines oscillator to obtain one horizontal bar with blocks of definition lines in vertical sequence. Besides it also controls the "gamma"-signal generator, to obtain one horizontal bar with a gamma signal. Because the appropriate circuits are also supplied with the circle pulse (c9), the said patterns are generated inside the circle area only.

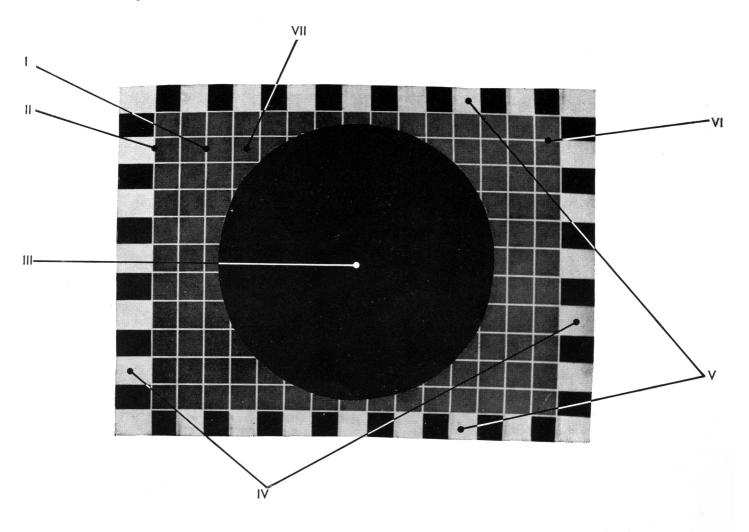

#### 3. Cross-Bar Gate

By means of a number of and-gates, several parts of the cross-bar pattern are generated.

The 3rd and-gate (from the top) produces the vertical white lines with the exception of the first one. The first vertical line is made in the 4th and-gate. Via a one-shot multivibrator, which determines the thickness of the lines (200 nsec.), both signals are fed to an adder circuit.

The 5th and 6th and-gate produce the horizontal white lines.

The 7th and 8th and-gates produce the black and white squares at the top and bottom of the pattern.

The 9th and-gate generates the black and white squares at the left – and right – hand side of the pattern.

All these signals are supplied to the adding circuit already mentioned.

The 10th gate, and the and/or gate, controls the adding circuit by means of the circle pulse ( $\sim$  c9), thus blanking a black circle area out of the cross-bar pattern when push-button "COMPL. PATTERN" is depressed. The grey amplifiers can each amplify only the pattern supplied to half of their white value. Together they produce a pattern with 100 % contrast.

The 1st and 2nd and-gate will, via an or-gate, control one of the amplifiers during the moments the pattern should be grey.

In an adding circuit, parts of the various patterns are added and applied to the output amplifiers (unit 16).

#### 4. Blank Pattern and Sawtooth Signal

On the printed wiring board of the output amplifiers a blank pattern-"generator" is mounted, the contrast-level of which can be adjusted with a potentiometer at the front of the apparatus. Moreover, a sawtooth generator producing a pattern, changing linearly from black to white, is also mounted on this unit. Both signals are fed to the adding circuit of unit 15.

#### D. Output Amplifiers

Both video outputs ("I" and "II") are fed by more or less identical circuits, containing, among others, a black level clipper and an output amplifier with low output impedance (75  $\Omega$ ). By means of additional circuits, the complete synchronizing and blanking signals are added.

The input circuit of amplifier I contains a potentiometer that enables the video signal (excl. sync.) at output I to be adjusted between 0.5 and 1  $V_{p-p}$  thus giving a possibility to vary the mixing-ratio of the internal pattern and a synchronized video signal connected to socket "EXT. VIDEO".

Moreover, it is possible to vary the sync. amplitude of the signal at output I between 0 and 200 % with control "SYNC. AMPL." on the front panel.

The circuit of amplifier II does not provide the above mentioned control of the signals, neither can an external video signal be added, in this case.

#### SERVICE INSTRUCTIONS

In the following chapters the circuitry of the units has been explained. The service-adjustments have been described at the end of the chapter concerned.

Please bear in mind the following notes:

- The unit to the checked or adjusted, should be placed on the "EXTENSION BOARD", unit 2 of the instrument.

- terminate parallel sockets with 75  $\Omega.\,$

- Apply the complete sync. signal to socket "SYNC-" and the complete blanking signal to socket "BLANKING-". These signals are derived from the PHILIPS TV-pulse generator PM 5530.

- The tolerances mentioned are factory tolerances which apply when-adjusting the instrument. They may differ from those shown in section "GENERAL", chapter "TECHNICAL DATA".

- The voltages shown in the diagram and the oscillograms published are measured with respect to terminal 12 (instrument connected to 220  $V\sim$ ).

- The d.c. voltages are measured with a PHILIPS d.c. voltmeter PM 2430.

- The a.c. voltages on unit 1 are measured with a PHILIPS a.c. voltmeter PM 2451.

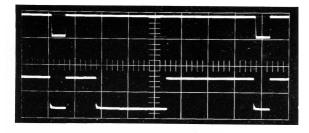

- The oscillograms are measured with a PHILIPS oscilloscope PM 3330 in connection with a PHILIPS double trace unit PM 3342 and a PHILIPS time base delay unit PM 3347.

- The oscillograms are photographed with a PHILIPS camera outfit PM 9300.

N.B. Disconnect the mains before exchanging printed wiring units!

Fig. IX-1 Connection-terminal blocks

### IX Unit 1

The power supply unit

The power-supply unit contains 3 stabilized rectifiers for the voltages -12 V, 6 V and 3 V.

The primary of the mains transformer has two separate windings (S1 + S2). They are connected in series when the apparatus is to be used with 230 V mains ( $\pm$  20 %) and in parallel in case of 115 V mains ( $\pm$  20 %).

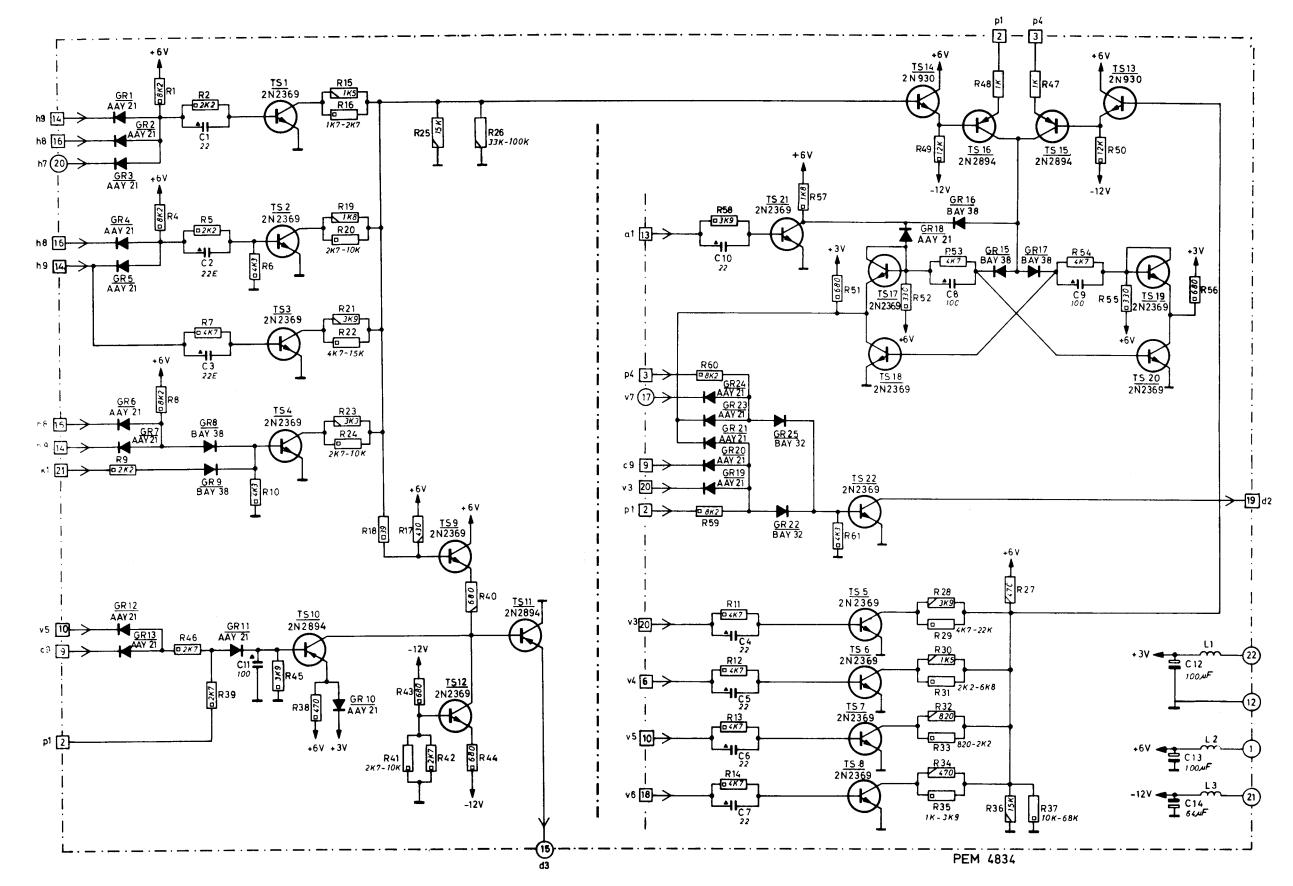

#### The 12-Volt rectifier

The voltage from winding S4 (17V) is rectified in diodes GR2 and stabilized by TS13. This transistor, which acts as a variable resistor, is so controlled that the –12 Volt output (terminals 18-19) is kept constant. The control current for TS13 is supplied by TS14 which is controlled by TS7. Here the emitter voltage is kept constant by Zener diode GR6. The base voltage of TS7 is dependent on the output voltage across R30, R29 and R31. If, for instance, this voltage becomes more negative, the emitter-base voltage of TS7 also becomes more negative, which, via emittor follower TS4, causes the current through TS13 to decrease.

This counteracts the voltage increase across R29-R30. The –12 Volt is adjusted by selecting the correct value of R31. TS1 operates as an overload protection. The base-emitter voltage is so selected by R8 that TS1 is cut-off. But if overloading takes place, the voltage across R11 increases and the emitter-base-voltage decreases, so that TS1 becomes conductive and the current through TS13 decreases.

The current for changing the magnetic state of the ferrite cores of the memory (approx. 800 mA) is taken from the -12 Volt (terminal 20). This current is tapped via TS12. TS12 has a heavy DC-feedback via R39. The AC-impedance is high due to the base decoupling of C5, which prevents the -12 Volt from being influenced by the strong current pulses.

#### The 6-Volt rectifier

The rectifying, stabilizing and the overload protection are the same as in the -12 Volt rectifier, only the control of the voltage variation is different. Here, the reference voltage is produced across the common emitter resistor R27. This voltage is kept constant by

the current through TS9, which is stabilized by Zener diode GR7. The base voltage of TS8 is dependent on the output voltage across R21, R22 and R23. The overload protection is effected by TS2 and is adjusted by R9.

#### The 3-Volt rectifier

This rectifier is built up as the 6-Volt rectifier. On account of the low output voltage, the base of TS11 is dependent on the voltage across R33, R35, R36 and Zenerdiode GR8. The 3-Volt output is adjusted by selecting the correct value of R33. Resistor R10 is selected for the overload protection of TS3.

The collector voltage of TS7...TS11 is produced by GR1 and stabilized by Zenerdiode GR5.

#### Checking and adjusting

Measuring equipment:

D.C. voltmeter: e.g. PHILIPS PM 2430.

Oscilloscope: e.g. PHILIPS PM 3230.

The stabilized voltages should not change more than 0.2 % with mains voltage variations of 180 to 280 V and 92 to 135 V respectively.

The following checks and adjustments are to be carried out at nominal mains voltage.

Push-button switch SK2 "COMPL. PATTERN" depressed.

Terminate "EXT. VIDEO OUT" with 75  $\Omega$ .

+ 6 V: this voltage is adjusted by selecting R23 (10  $\Omega$  – 470  $\Omega$ )

+ 3 V: this voltage is adjusted by selecting R33 (560  $\Omega$  – 4.7 k $\Omega$ )

= 12 V: this voltage is adjusted by selecting R31 (2.7  $k\Omega$  = 15  $k\Omega$ ).

The base-emitter voltage of TS1...TS3 should be 200 mV, -20 % + 10 %.

This voltage is adjusted by selecting R8 (220  $\Omega$  = 820  $\Omega$ ), R9 (150  $\Omega$  = 1.5 k $\Omega$ ) and R10 (330  $\Omega$  = 4.7 k $\Omega$ ) respectively.

Check the ripple voltages at a mains voltage of 180 V (voltage selector in position "230 V").

$$\begin{array}{c} \text{At} & + 6 \, \text{V:} \\ & + 3 \, \text{V:} \\ & - 12 \, \text{V:} \end{array} \right\} \begin{array}{c} < 2 \, \text{mV}_{pp} \\ \text{(without signals from a PM 5530)} \end{array}$$

Fig. IX-2 Printed wiring board, Power supply, Unit 1

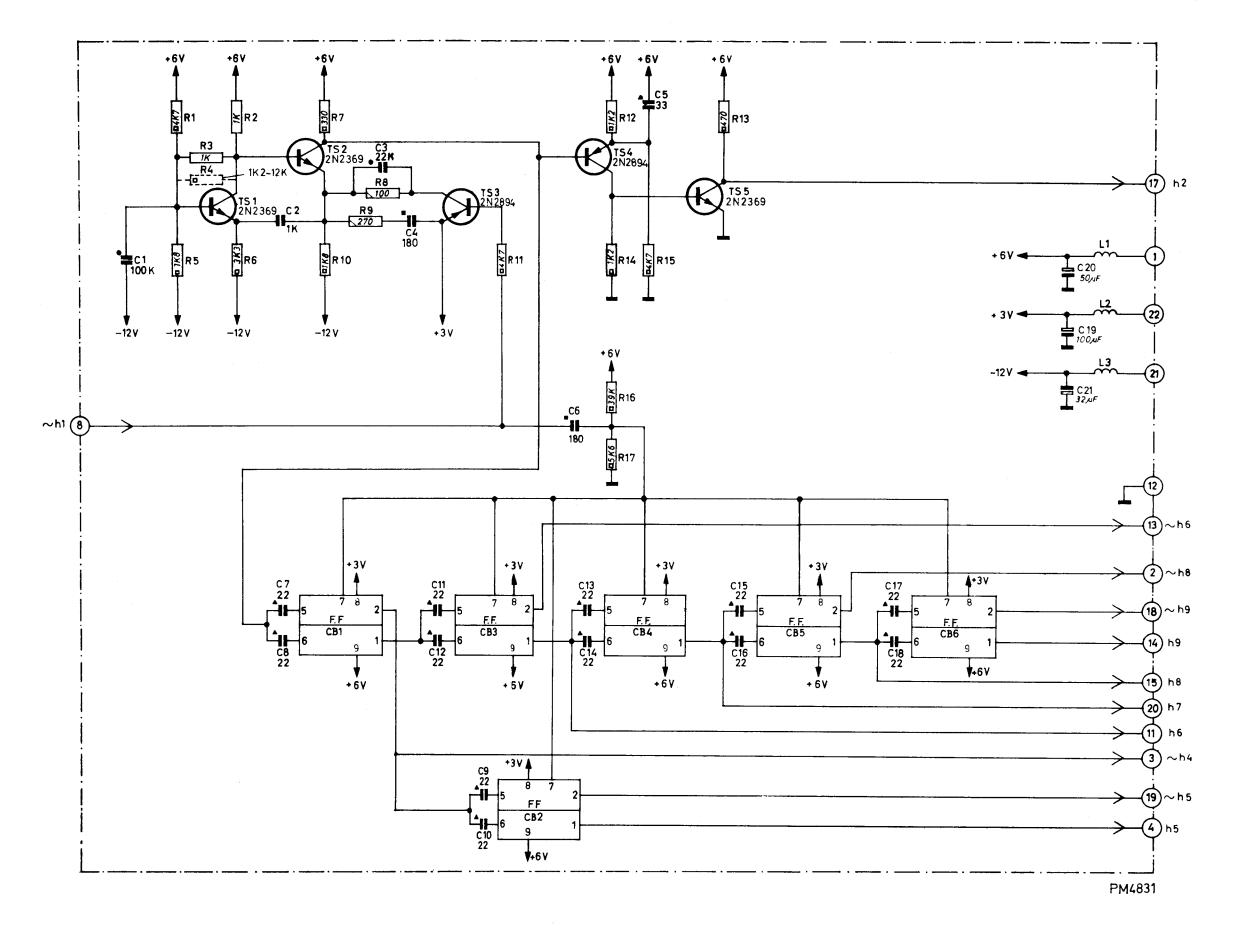

Fig. IX-4 Circuit diagram, power-supply, Unit

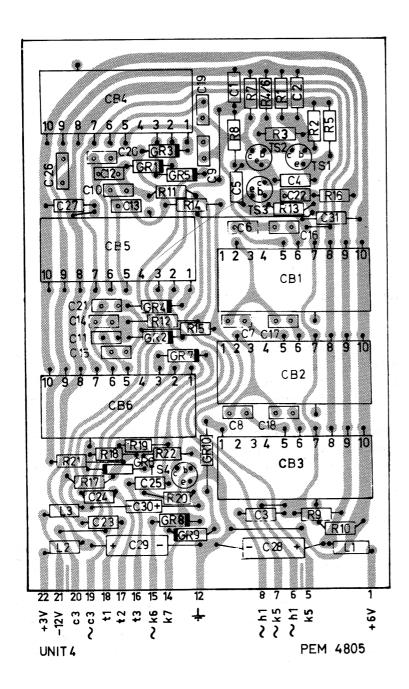

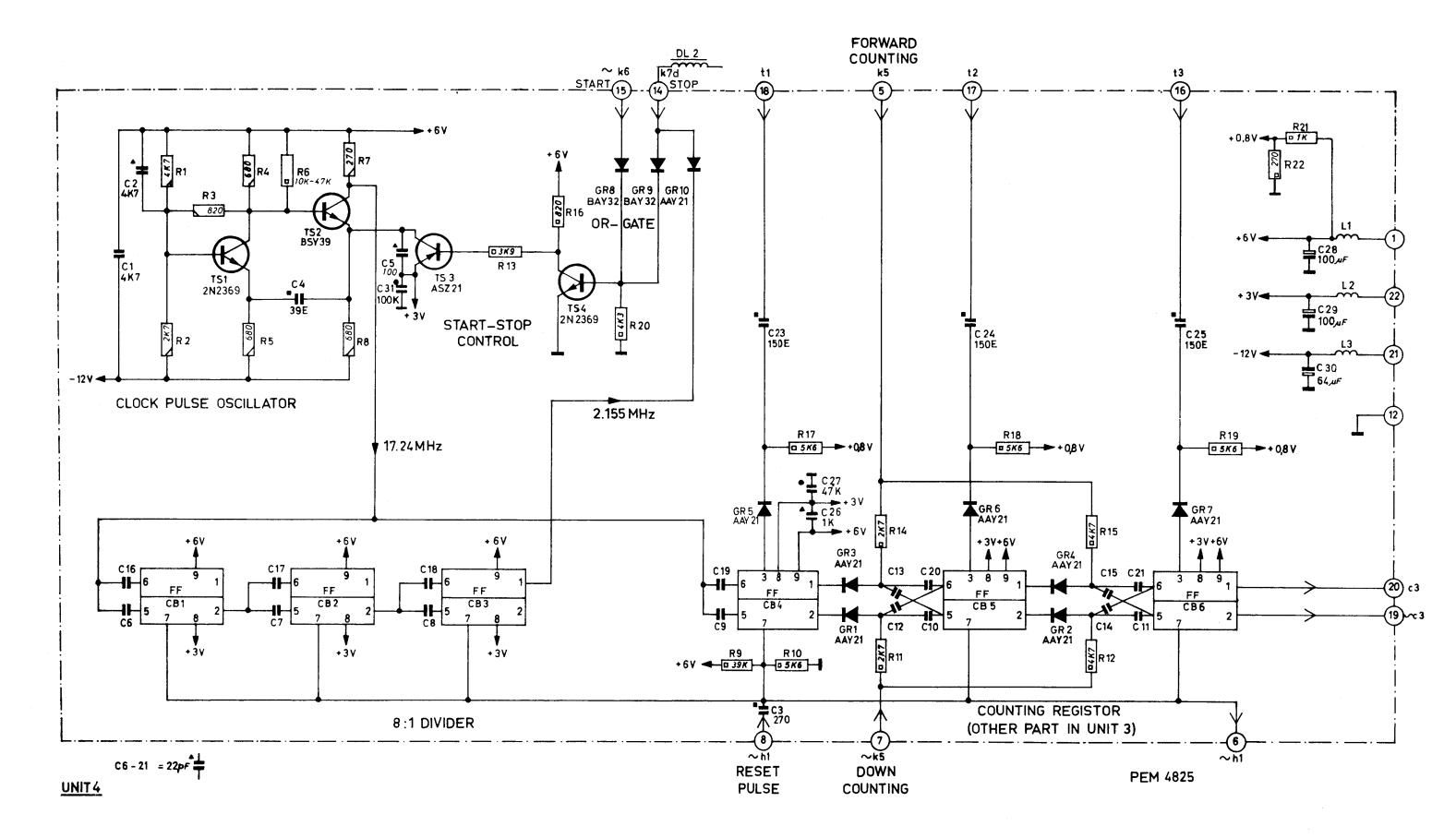

### X Units 3 and 4

The circle register

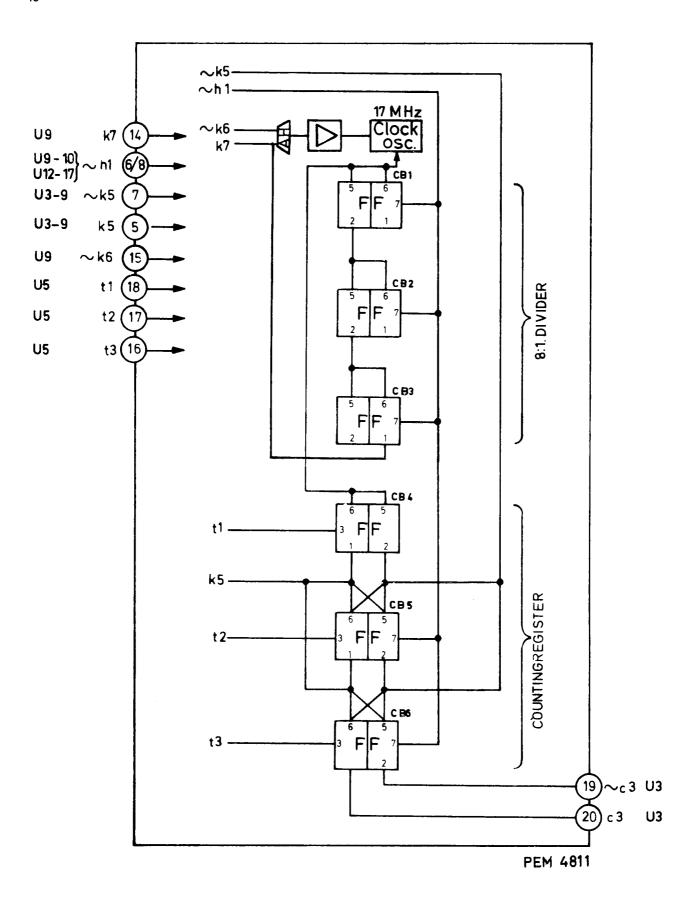

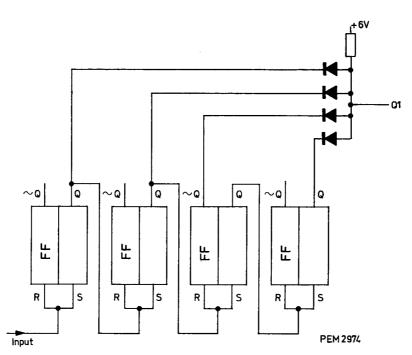

The circle register is accommodated on units 3 and 4. It consists of a 17 MHz clock-pulse oscillator and an 8-bit counting register for generating the circle informations.

#### The 17 MHz clock-pulse oscillator (unit 4)

Transistors TS1 and TS2 form an emitter-coupled oscillator.

The frequency is dependent on the value of R4 and R6. The circle register is controlled by the output voltage of the oscillator, which is taken from the collector of TS2.

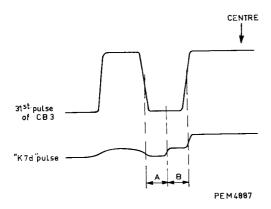

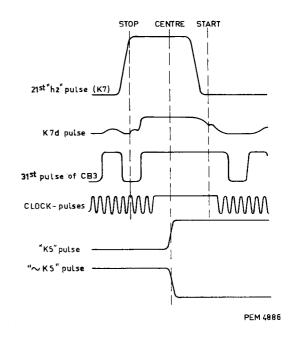

The " $\sim$  k6" pulse actuates the oscillator within the periods limited by the envelope of the circle, while the "k7d" pulse stops and starts the oscillator during the periods the counting sense of the register is reversed. The counting sense of the register is reversed at the centre of the circle. This means that the register is in a well-defined state when the clock-pulse oscillator is stopped. The oscillator is stopped after an exact number of oscillations.

This is effected by means of the 3-bit divider CB1...CB3 which supplies only one output pulse every eight oscillator-clock pulses.

Just before the centre line, the 31st output pulse of CB3 is selected by the "k7d" pulse, which determines the stop and start of the oscillator. The oscillator is stopped after the 31st output pulse of CB3 with a small delay. This delay is determined by the 8:1 divider CB1...CB3 ( $8\times31=248$  periods), and a small constant delay of OR-gate GR8...GR10 and transistors TS3 and TS4.

The oscillator is started again at the trailing edge of the "k7d" pulse (see Fig. X-2).

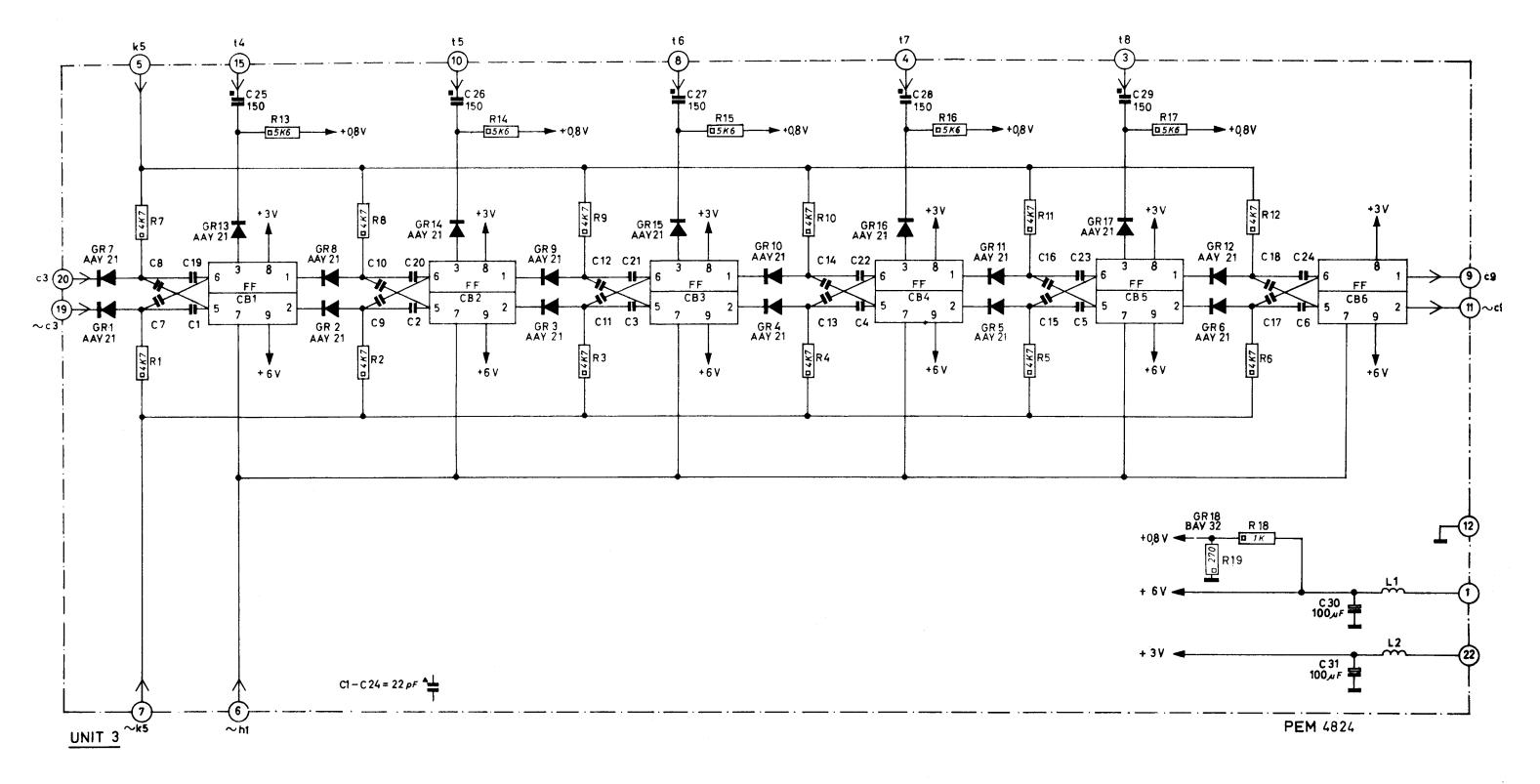

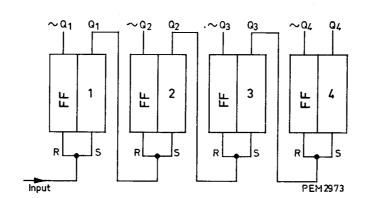

#### The counting register

The eight-bit register consists of the circuit blocks CB4...CB6 in unit 4 and CB1...CB6 in unit 3.

It can be set to zero (reset), set to down or forward-counting and set by means of the read out pulses from the memory (preset).

The function of the register is a follows:

At the beginning of a line the register is set zero by the " $\sim$  h1" pulse. The counting direction of the register is determined by the "k5" and " $\sim$  k5" pulses so that it is down-counting up to point C (see Fig. X-1).

Before the clock-pulse oscillator starts, the read-out pulses t1...t8 of the memory are applied to the register via C23...C25 in unit 4 and C25...C29 in unit 3.

At point A (Fig. X-1) the clock-pulse oscillator is started by the " $\sim$  k6" pulse. At the same time the register is set to down-counting by the read-out digit from the memory, which has been set into the register. When the register passes zero circuit block CB6 delivers the "c9" an " $\sim$  c9" pulses. The leading edge of this pulse corresponds to the front envelope of the circle "B" (Fig. X-1). Just before the centre line "C" (Fig. X-1) the clock-pulse oscillator is stopped as described above. Then the counting direction of the register is reversed to forward-counting by the "k5" and " $\sim$  k5" pulses and the clock-pulse oscillator is started again by the trailing edge of the "k7d" pulse (see Fig. X-2). The register then counts forwards to zero during the right half of the circle. When again passes zero it will have counted exactly the same number of periods as during the left half of the circle. When passing zero circuit block CB6 delivers the trailing edge of the "c9" and " $\sim$  c9" pulses which correspond to the back envelope of the circle "D" (Fig. X-1). The "c9" and " $\sim$  c9" pulses are applied to the units 13. 14 and 15 to be combined with the rest of the test pattern.

#### Checking and adjusting

Measuring equipment:

Oscilloscope e.g. PHILIPS PM 3330 With dual-trace-Y amplifier e.g. PHILIPS PM 3342 Monitor e.g.

#### Clock-frequency (approx. 17 MHz)

Connect the A amplifier of the oscilloscope to point 1 of CB3 and the B amplifier to terminal 17.

Trigger with the "h1" pulse (terminals 4 of unit 17) and display the centre of the T.V. line.

The oscillogram should be as shown in the figure below.

The width of A and B should be equal.

If not, select another value for R6 (10 k $\Omega$  . . . 47 k $\Omega$ ).

#### Position of the front envelope of the circle

Connect the monitor to BU5 (BU2) "VIDEO II OUT". Adjust the monitor so that the complete pattern is displayed. The circle should start exactly at the transient of the black-white steps in the middle of the circle. If not, select another value for R32 in unit 9 (4.7 k $\Omega$ ... 12 k $\Omega$ ).

Fig. X-2 Pulse diagram

k5

5 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

$\sim$  k6

1 V/cm  $8 \mu s/cm$  reference: line sync.

$\sim$  h1

5 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

$\sim$  k5

5 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

k7

1 V/cm 8 μs/cm reference: line sync.

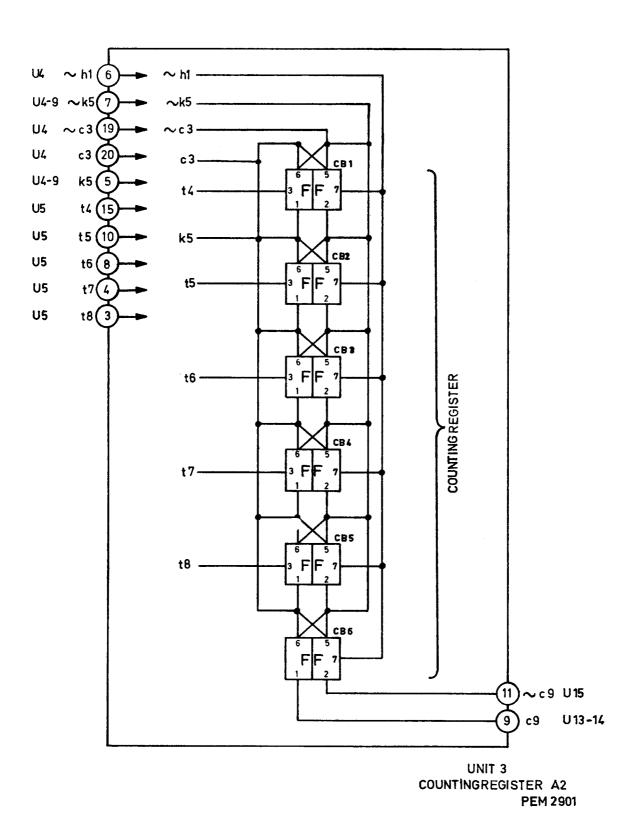

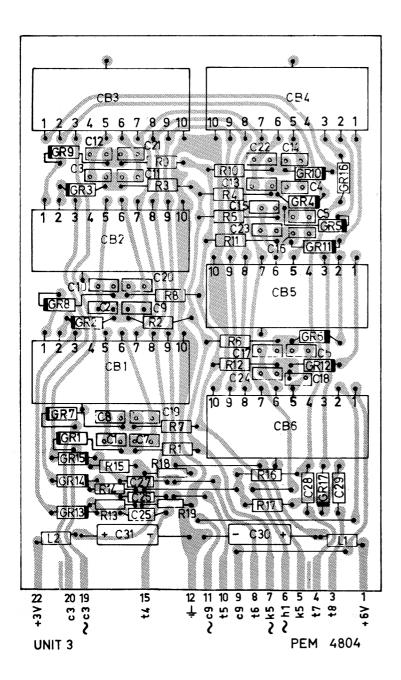

Fig. X-4 Block-diagram, counting register, Unit 3

Fig. X-5 Printed wiring board, counting register, Unit 3

Fig. X-7 Block-diagram, circle register, Unit 4

Fig. X-9 Circuit diagram, circle register, Unit 4

# XI Unit 5

#### The memory

The memory consist of a ferrite core matrix, the readout circuits TS1 . . . TS8 and strobe amplifier TS9.

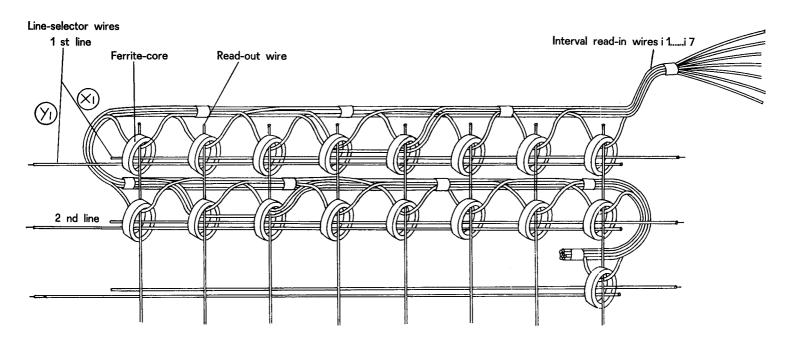

#### The ferrite core matrix

Each interval covers 22 lines, while the information for each line is a binary figure of 8 bits. The memory is formed as a matrix of 22 lines, each containing 8 ferrite cores.

These cores are, from line to line, turned  $90^{\circ}$  to obtain read-out pulses with the same polarity at the vertical read-out wires.

The interval read-in wires (i1...i7) pass the cores where the binary figure should be "1", and by-pass them if the figure should be "0" (see Fig. XI-1). Each line consist of line-selector wires X1...X4 and Y1...Y6. Each wire is driven with half current pulses in the same phase so that each of these combinations can select one line.

With the four X-wires and the six Y-wires 24 combinations are possible, which represent a selection of 24 lines (French system). However, for the 625-lines system the first 22 combinations are used, while for the 525-lines system only the first 18 combinations are used.

Before a read-in takes place, all cores are automatically set to zero by the preceding read-out pulse.

On reading-in a current flows through one of the 7 selected interval wires (i1...i7) to reverse the magnetic state of the corresponding cores. The cores not being passed, are not set.

The reading-in of a new interval is made at the moment that the middle of the last line of the preceding interval is produced by the circle register.

At the beginning of each line of an interval, the half-current pulses, which pass through the X and Y-line selector wires, cannot separately cause the cores to reverse their magnetic state. If these half-current pulses in both wires coincide, they set the cores of the line concerned to zero. When the cores are set to zero, a voltage on the vertical read-out wires is in-

duced and passed on to the read-out amplifiers TS1.. TS8. After amplification and pulse shaping the latter supply the pulses "t1...t8" which are used for setting the respective flip-flops of the counting register (units 3 and 4). At the beginning of the next line the X- and Y-wires again carry half-current pulses, so that the information for this line is also transferred to the counting register. This process is repeated line after line until all information for the 22 lines is transferred. At the middle of the 22nd line, the information of the next interval is read in and the setting to zero is made.

### The read-out amplifiers

These amplifiers are transformer-coupled to the readout wires by  $T1 \dots T8$ .

The ratio is 1:10 and directed so that the read-out pulses saturate the succeeding transistors TS1...TS8. As the read-out wires are threaded through all cores, all induced signals are amplified. This implies that the unwanted signals from the cores through which only half-current pulses are flowing will also be amplified and create false pulses. However, because of the nonlinear hysteresis loop of the cores only the full current pulses are delayed about 0.75  $\mu$ s. So these correct pulses will be separated from the false ones by the gating of strobe amplifier TS9.

The "z" pulse, originating from the strobe generator (U6), is also delayed 0.75  $\mu s$  by C1-R20 and saturate TS9. When TS9 is saturated, the base levels of TS1...TS8 are at emitter level of TS9 and as a result of this TS1...TS8 are actuated by positive going pulses from the transformers.

During this time negative going pulses (t1...t8) appear at the collectors of TS1...TS8. These pulses are used for setting the counting register in units 3 and 4.

### Checking and adjusting

Measuring equipment:

Oscilloscope: e.g. PHILIPS PM 3330.

### Read- in currents (i1 . . . i7)

Connect the oscilloscope across R22-R23. Check that the individual pulses are approx. 11  $V_{\rm p-p}$  (corresponding to approx. 755 mA - 800 mA).

If not, select R23 (68  $\Omega$  – 150  $\Omega$ ). If the control range of R23 is not sufficient check the corresponding read-in amplifier (unit 8).

### Read- in currents (X and Y)

Connect the oscilloscope across R24-R25 for the Y pulse and across R26-R27 for the X pulse. Check that the individual pulses are between 13.5  $V_{p-p}$  and 14  $V_{p-p}$  (corresponding to approx. 380 – 400 mA). If not, select R25 (270  $\Omega-470~\Omega)$  for the Y pulses and R27 (270  $\Omega-470~\Omega)$  for the X pulses. If the control ranges of these resistors are not sufficient, check the corresponding read-in amplifier (unit 6).

Fig. XI-1 Principle of the memory

Fig. XI-3 Block-diagram, memory, Unit 5

Fig. XI-4a Printed wiring board, memory (A version), Unit 5

Fig. XI-4b Printed wiring board, memory (E version), Unit 5

Fig. XI-5 Circuit diagram, memory, Unit 5

From version /06 the following is modified:

— GR1 is of the type AAZ15 (4822 130 30229)

— C1 has become 150pF

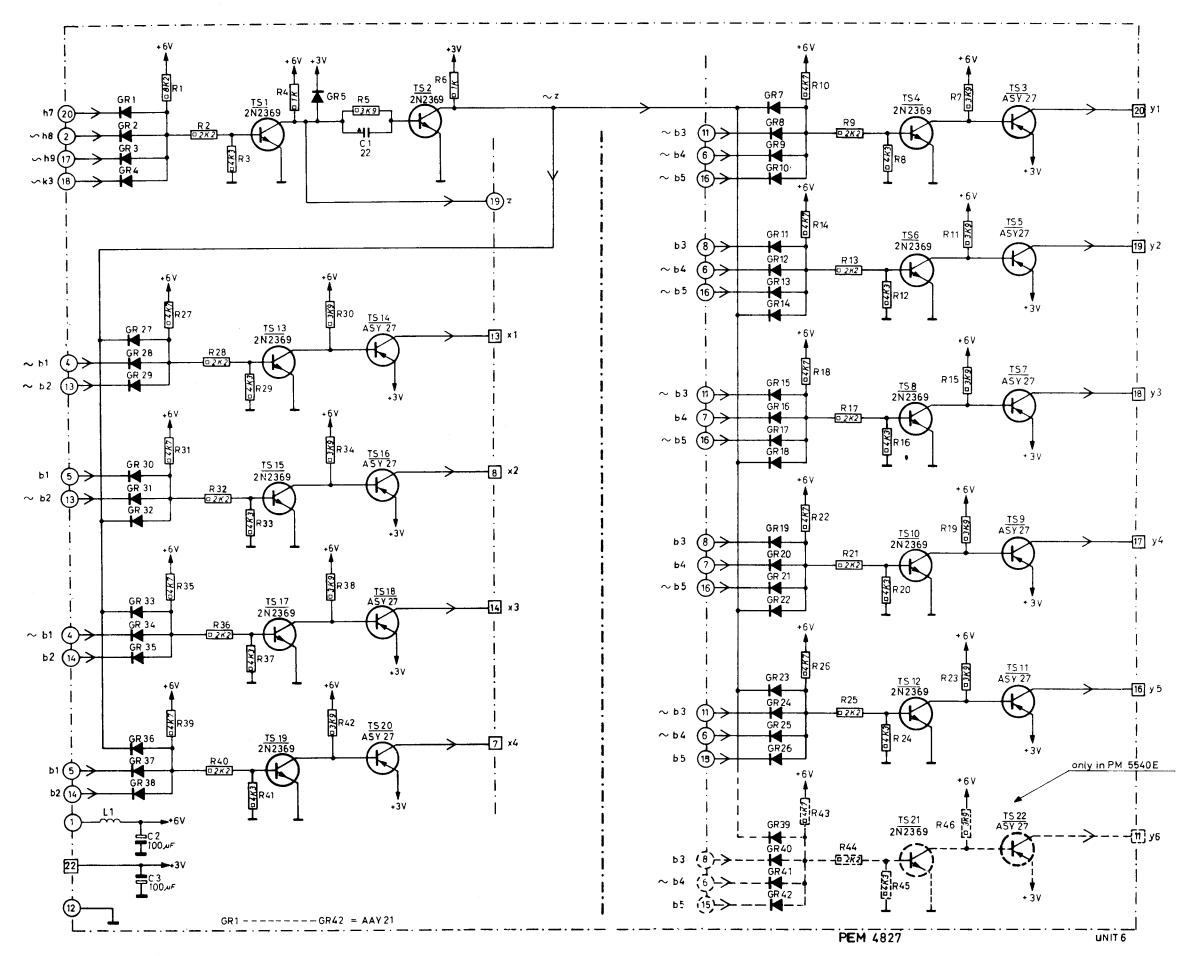

# XII Unit 6

## The line decoder

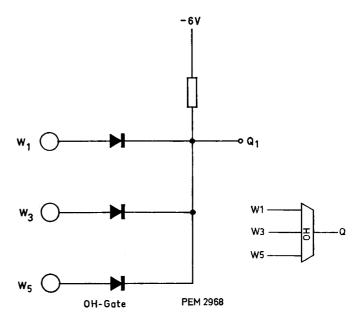

The decoder consists of the AND-gates GR27...GR38 for the X-read-in pulses and the AND-gates GR7...GR26 and GR39...GR42 for the Y-read-in pulses. These gates are succeeding by the read-in amplifiers TS3...TS22. The read-in current is about 400 mA. In the AND-gates, the X- and Y-pulses are produced by combining the pulses from the flip-flops of the line selector register.

The table below shows the composing of the X- and Y-pulses for reading- in the 22 lines.

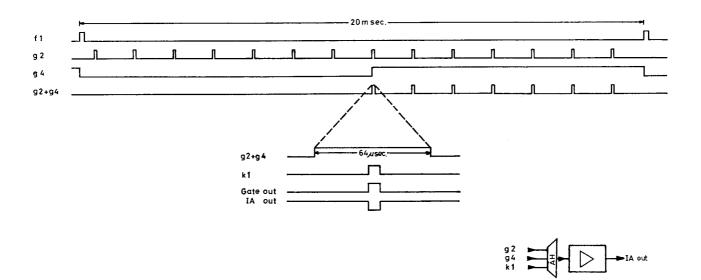

### Strobe generator

This circuit consists of an AND-gate GR1 ... GR4 and the amplifiers TS1 and TS2.

In the AND-gate the "z" pulse is produced by combining suitable pulses from the horizontal divider (unit 10) and the horizontal decoder (unit 9).

The "z" pulse is transferred to the strobe amplifier in unit 5, while the " $\sim$ z" pulse is used for control of the X and Y AND-gates.

### Line selector register

| number | CB5 | CB4 | CB3 | CB2 | CB1 | $x_1$ | $x_2$ | $x_3$ | $X_4$ | <b>y</b> <sub>1</sub> | <b>y</b> <sub>2</sub> | <b>y</b> <sub>3</sub> | У4 | <b>y</b> 5 | У <sub>6</sub> * |

|--------|-----|-----|-----|-----|-----|-------|-------|-------|-------|-----------------------|-----------------------|-----------------------|----|------------|------------------|

| 1      | 0   | 0   | 0   | 0   | 0   | 1     |       |       |       | 1                     |                       |                       |    |            |                  |

| 2      | 0   | 0   | 0   | 0   | 1   |       | 1     |       |       | 1                     |                       |                       |    |            |                  |

| 3      | 0   | 0   | 0   | 1   | 0   |       |       | 1     |       | 1                     |                       |                       |    |            |                  |

| 4      | 0   | 0   | 0   | 1   | 1   |       |       |       | 1     | 1                     |                       |                       |    |            |                  |

| 5      | 0   | 0   | 1   | 0   | 0   | 1     |       |       |       |                       | 1                     |                       |    |            |                  |

| 6      | 0   | 0   | 1   | 0   | 1   |       | 1     |       |       |                       | 1                     |                       |    |            |                  |

| 7      | 0   | 0   | 1   | 1   | 0   |       |       | 1     |       |                       | 1                     |                       |    |            |                  |

| 8      | 0   | 0   | 1   | 1   | 1   |       |       |       | 1     |                       | 1                     |                       |    |            |                  |

| 9      | 0   | 1   | 0   | 0   | 0   | 1     |       |       |       |                       |                       | 1                     |    |            |                  |

| 10     | 0   | 1   | 0   | 0   | 1   |       | 1     |       |       |                       |                       | 1                     |    |            |                  |

| 11     | 0   | 1   | 0   | 1   | 0   |       |       | 1     |       |                       |                       | 1                     |    |            |                  |

| 12     | 0   | 1   | 0   | 1   | 1   |       |       |       | 1     |                       |                       | 1                     |    |            |                  |

| 13     | 0   | 1   | 1   | 0   | 0   | 1     |       |       |       |                       |                       |                       | 1  |            |                  |

| 14     | 0   | 1   | 1   | 0   | 1   |       | 1     |       |       |                       |                       |                       | 1  |            |                  |

| 15     | 0   | ·Ť  | 1   | 1   | 0   |       |       | 1     |       |                       |                       |                       | 1  |            |                  |

| 16     | 0   | 1   | 1   | 1   | 1   |       |       |       | 1     |                       |                       |                       | 1  |            |                  |

| 17     | 1   | 0   | 0   | 0   | 0   | 1     |       |       |       |                       |                       |                       |    | 1          |                  |

| 18*    | 1   | 0   | 0   | 0   | 1   |       | 1     |       |       |                       |                       |                       |    | 1          |                  |

| 19*    | 1   | 0   | 0   | 1   | 0   |       |       | 1     |       |                       |                       |                       |    | 1          |                  |

| 20*    | 1   | 0   | 0   | 1   | 1   |       |       |       | 1     |                       |                       |                       |    | 1          |                  |

| 21*    | 1   | 0   | 1   | 0   | 0   | 1     |       |       |       |                       |                       |                       |    |            | 1                |

| 22*    | 1   | 0   | 1   | 0   | 1   |       | 1     |       |       |                       |                       |                       |    |            | 1                |

<sup>\*)</sup> Not in PM 5540 A

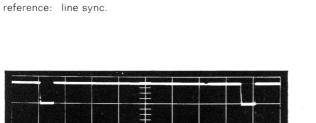

z  $$2\ensuremath{\text{V/cm}}$$   $8\ensuremath{\,\mu\text{s/cm}}$  reference: line sync.

2 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

$\sim$  z

Gate for strobe amp.

Unit 6

PEM 2925

Fig. XII-2 Gate for strobe amplifier

Fig. XII-3 Block-diagram, line decoder, Unit 6

Fig. XII-5 Circuit diagram, line decoder, Unit 6

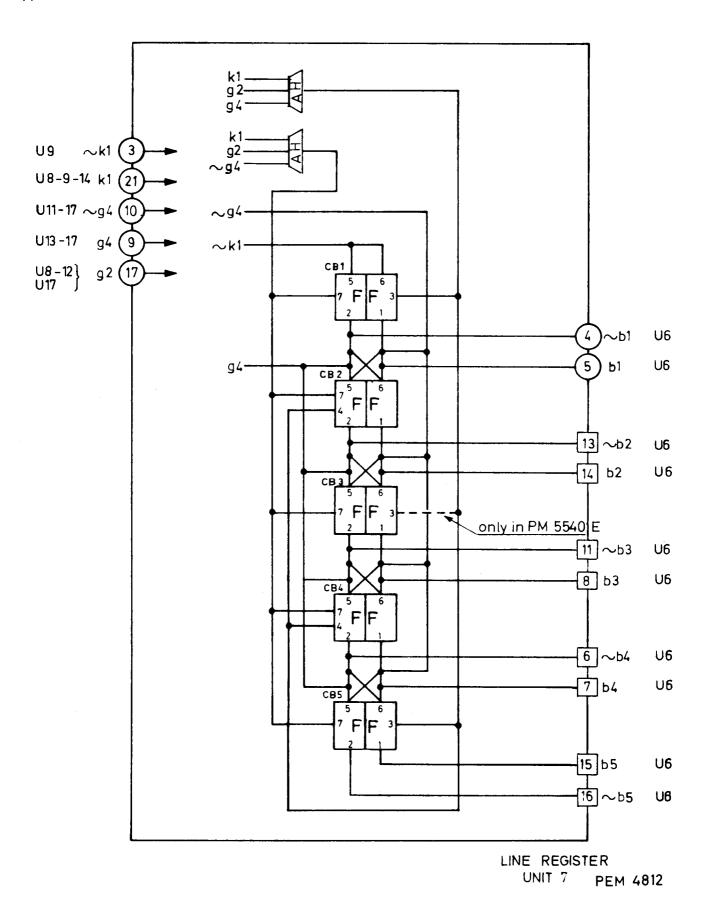

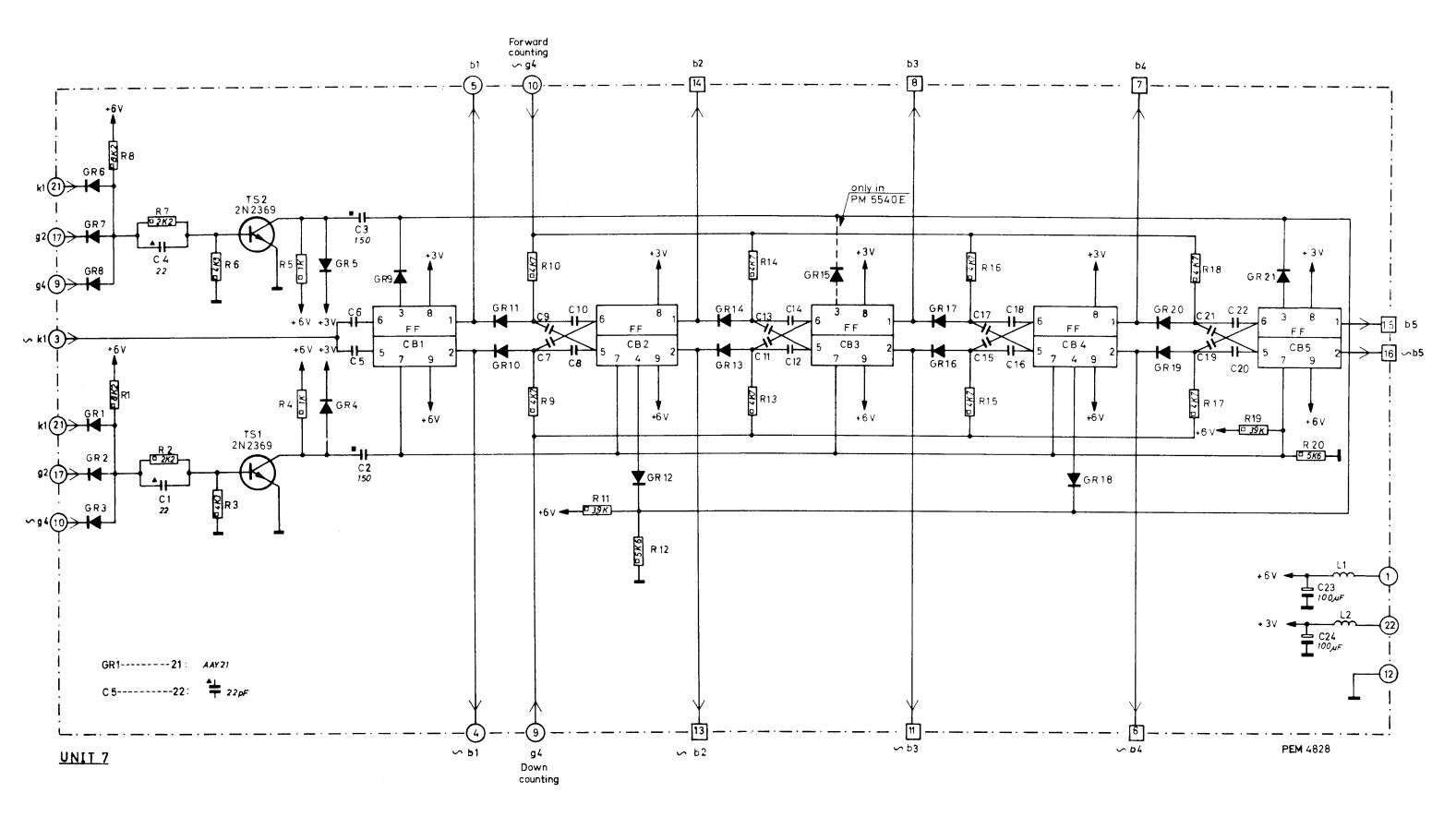

# XIII Unit 7

### The line-selector register

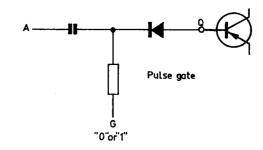

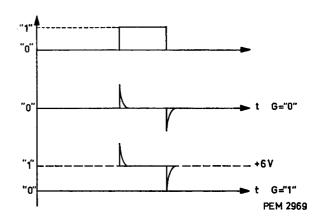

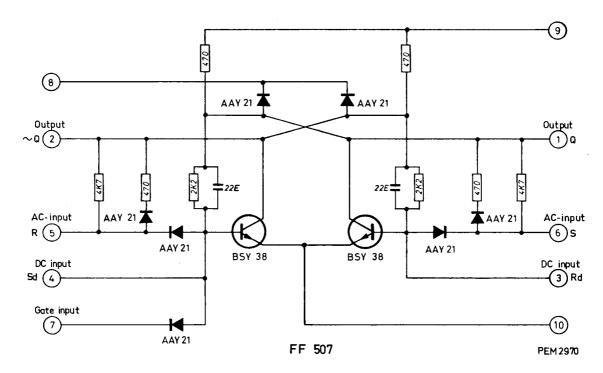

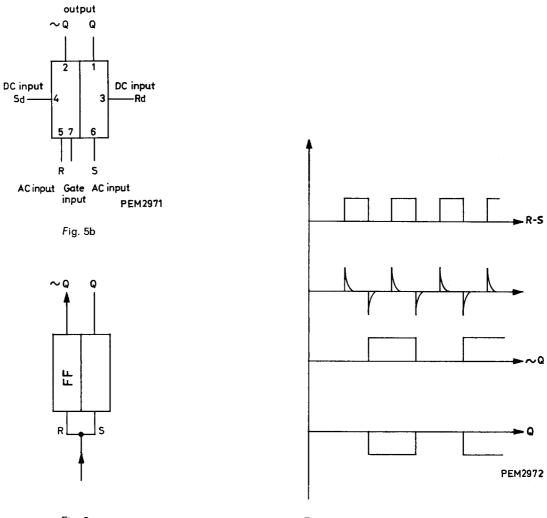

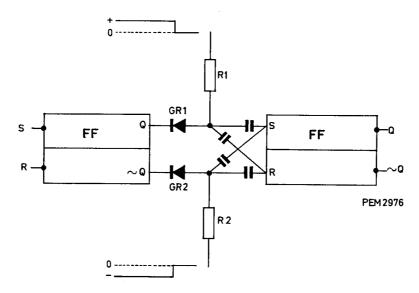

This register consists of the 5 cascade connected flipflops CB1...CB5, the AND-gates GR1...GR3 and GR6...GR8 succeeded respectively by the amplifiers TS1 and TS2.

The register can be set to zero (reset), set to 21<sup>1</sup>) (preset) and set to change over from forward to down-counting or vice versa.

The resetting is effected by the "k1" pulse combined with the "g2" and " $\sim$  g4" pulses via GR1 ... GR3 and TS1 to input 7 of CB1 ... CB5. The setting to 21 is made by the "k1" pulse combined with the "g2" and "g4" pulses via GR6 ... GR8 and TS2 to input 3 of CB1, CB3 and CB5.

The setting to forward- or down-counting is effected by the " $\sim$  g4" and "g4" pulses respectively.

The functioning of the register is as follows.

During the last line of an interval in the upper half of

the pattern, the register is set to zero. During each succeeding line the register counts forward the " $\sim k1"$  pulses. After the register has counted to  $21^{\rm l}$ ), the last line of an interval is reached, and the reset will be made if the succeeding interval is still in the upper half of the pattern.

If the succeeding interval is in the lower half of the pattern, the register will be preset to  $21^1$ ) instead of set to zero, and for each succeeding line the register will count down the "k1" pulses. At zero, presetting 21 will be read-in again, and the process will be repeated until the upper half of the next field occurs. Then the setting to zero with forward-counting will be arranged. Pulses " $\sim$  94" and "94" inform the register concerning the upper half or lower half respectively of the pattern. Outputs "b1 ... b5" and " $\sim$  b1 ...  $\sim$  b5" of the register are supplied to the line decoder (unit 6) to give the 10 read-in pulses X1 ... X4 and Y1 ... Y6²).

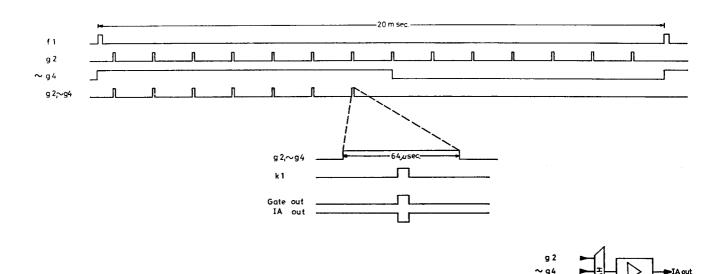

pulse gen: for pre -selector of line registor Unit 7 PEM2924

Fig. XIII-1 Pulse generator, pre-selector of line register

Fig. XIII-2 Pulse generator, pre-selector of line register

Fig. XIII-3 Block-diagram, line register, Unit 7

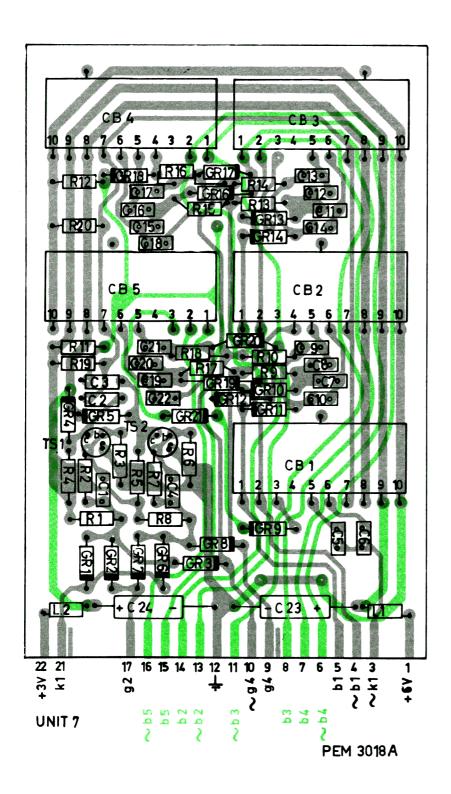

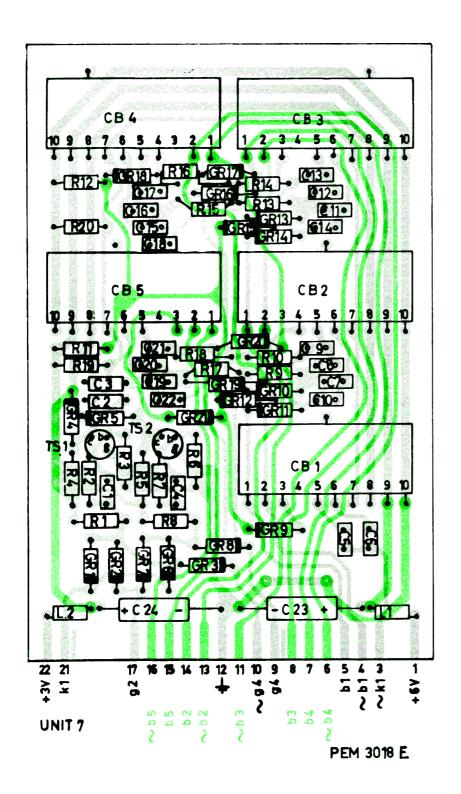

Fig. XIII-4a Printed wiring board, line register (A version), Unit 7

Fig. XIII-4b Printed wiring board, line register (E version), Unit 7

Fig. XIII-5 Circuit diagram, line register, Unit 7

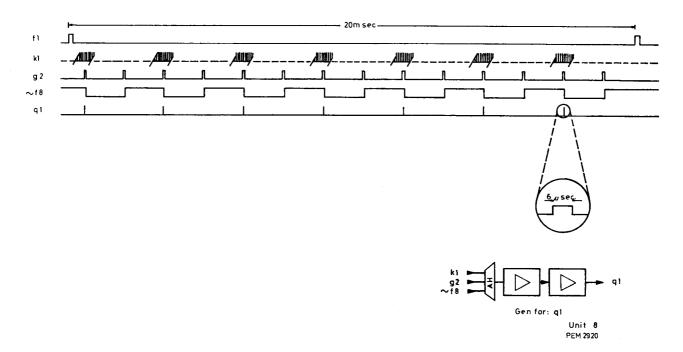

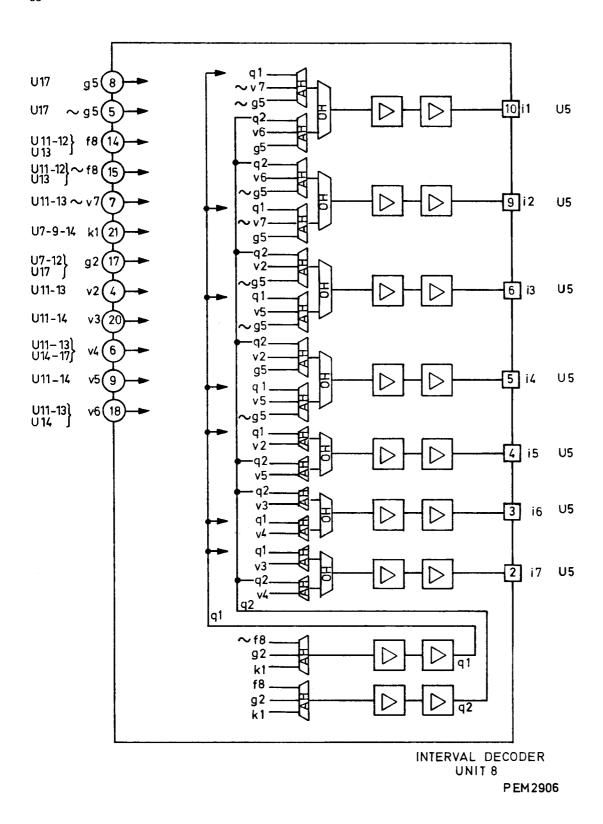

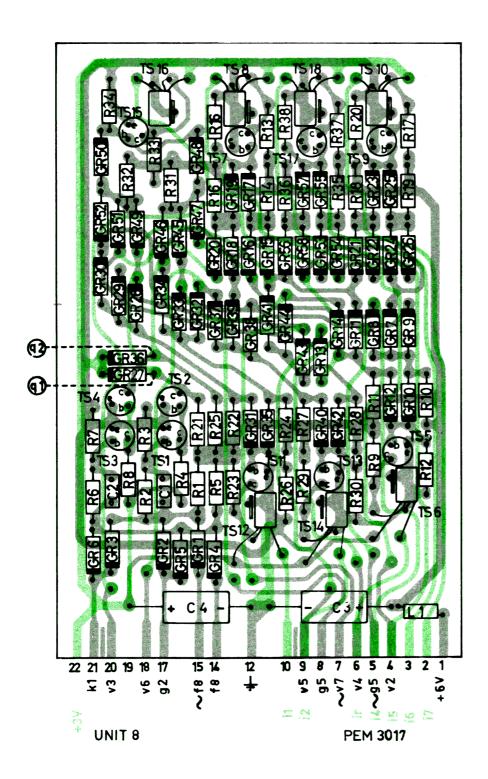

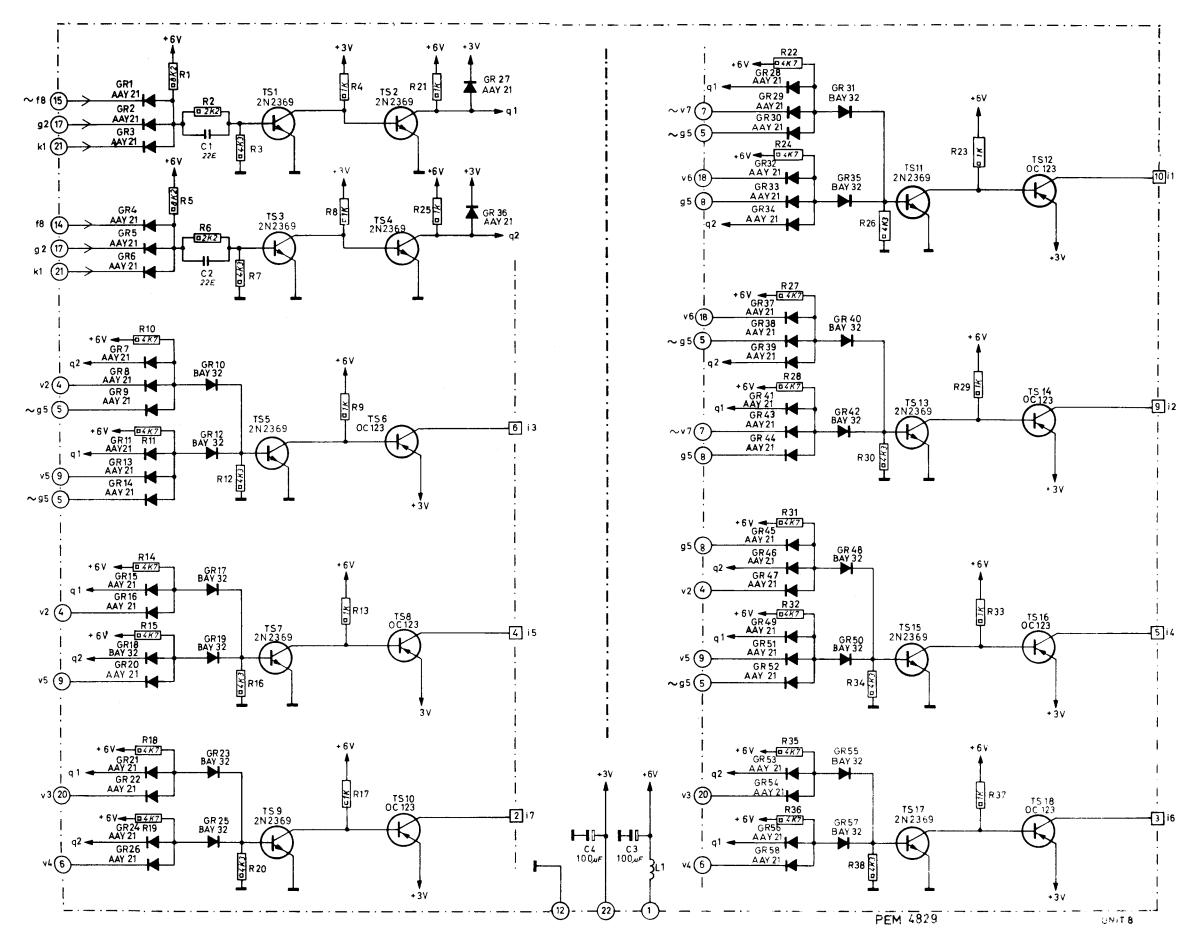

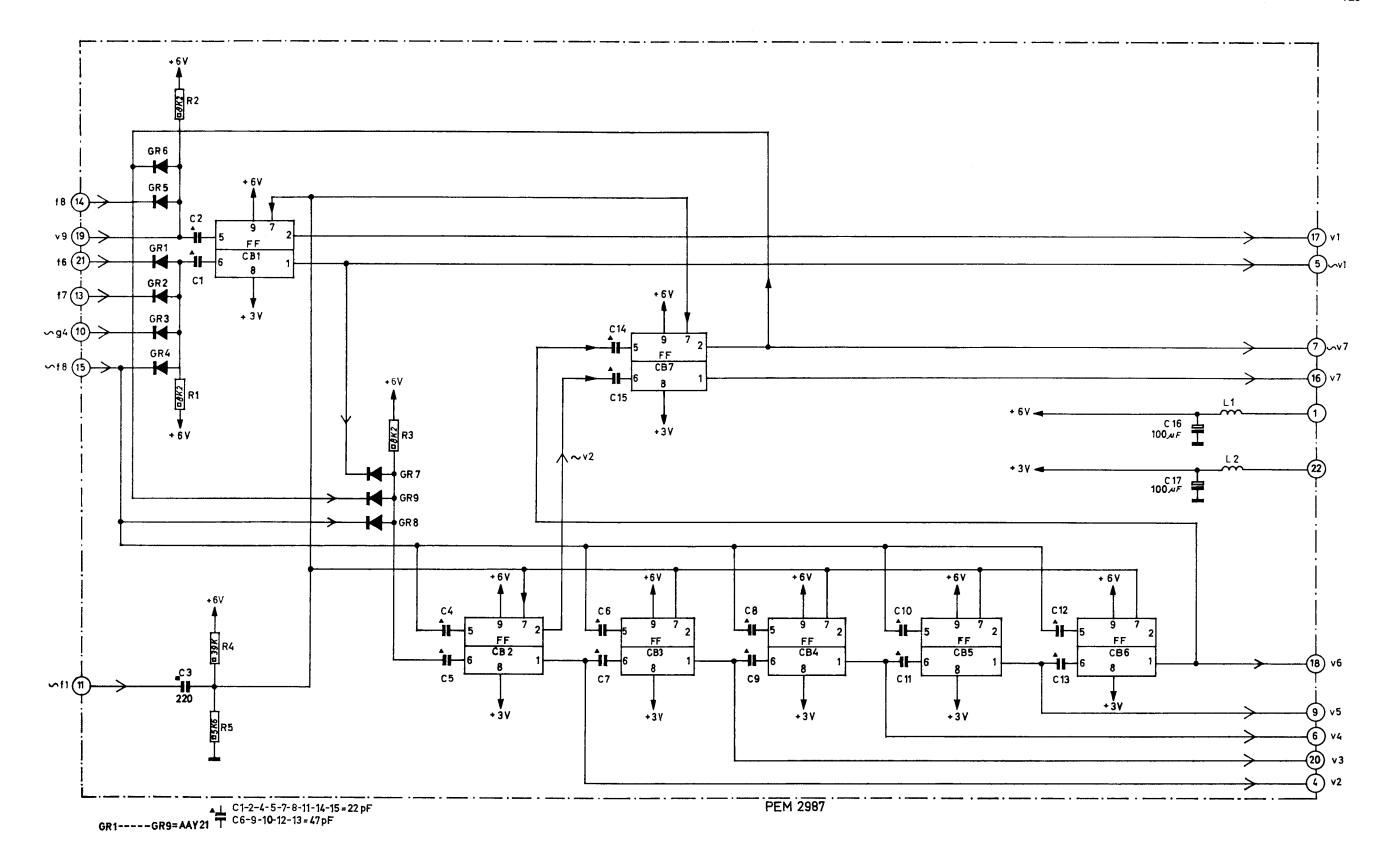

# XIV Unit 8

#### The interval decoder

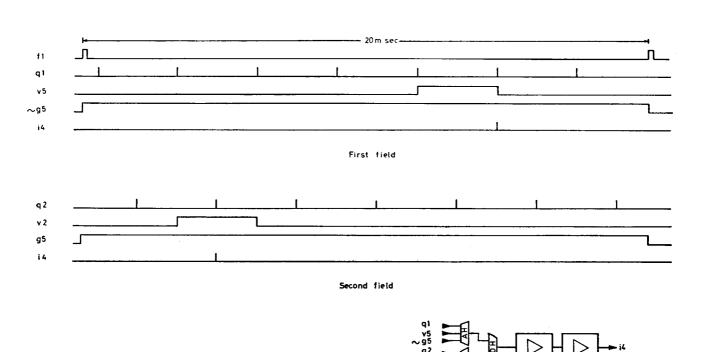

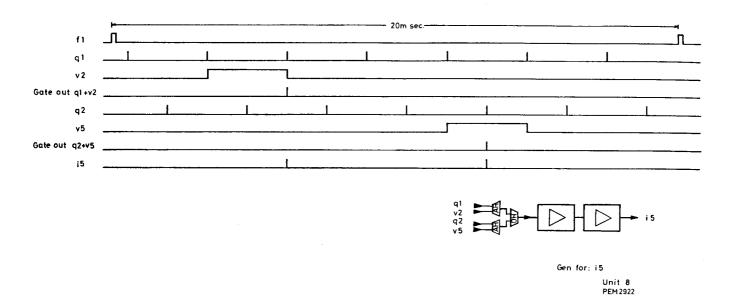

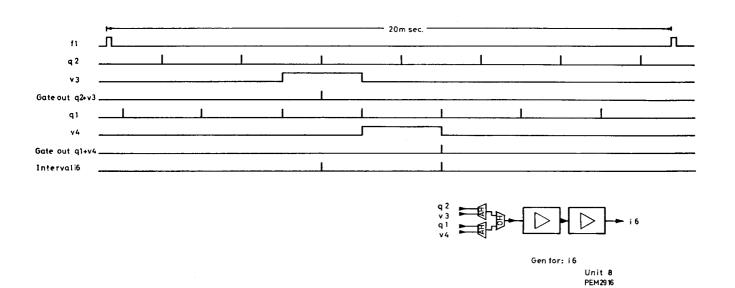

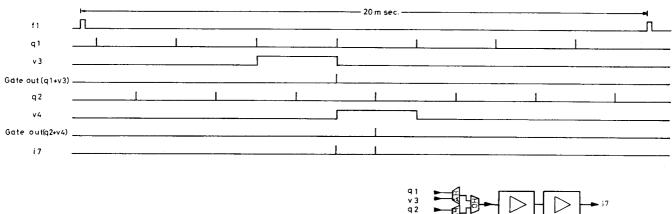

As mentioned in the description of the principle of the circle generator, the circle information will be deduced from seven different read-ins to the ferrite core memory.

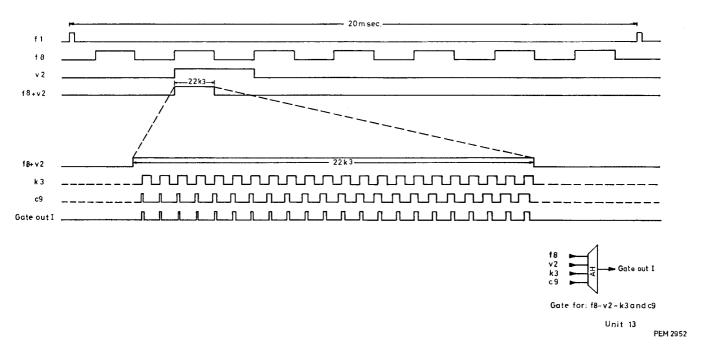

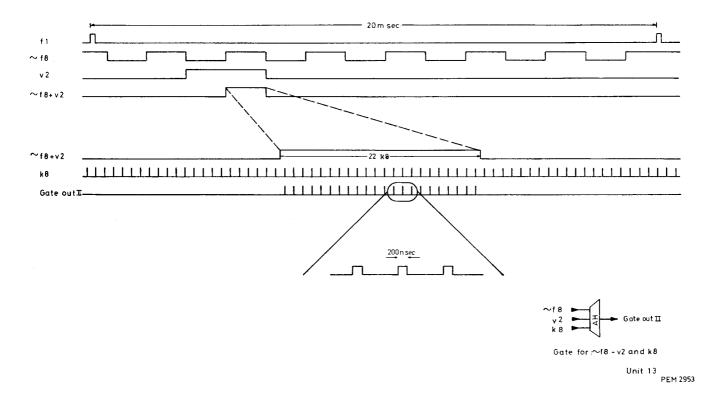

The sequence of this information is determined by these read-in pulses. The pulses are supplied by the read-in amplifiers TS5...TS18 and controlled by the AND- and OR-gates GR7...GR26, GR28...GR35 and GR37...GR58. To simplify these gates, the following pulses are combined in the AND-gates GR1-GR3 and GR4...GR6.

The ''k1'' pulse, controlling the moment and duration of the read-in (6  $\mu s). \label{eq:k1}$

The "g2" pulse, opening the gate during the last line of the interval.

The "f8" and " $\sim$  f8" pulses, producing the seven different intervals. The intervals number 5, 6 and 7 however, are used two times in one field.

The resulting pulses "q1" and "q2", are applied to the read-in gates.

The "g5" and " $\sim$  g5" pulses are distinguishing between the two fields ("g5" for the first field and " $\sim$  g5" for the second one).

The  $^{\prime\prime}\!\!\sim\! v7^{\prime\prime}$  pulse opens the gate withing the circle area.

The "v2"..."v6" pulses determine the moment at which the read-in concerned is made. The read-in currents, having a duration of 6  $\mu$ s, are of a magnitude of 755 mA.

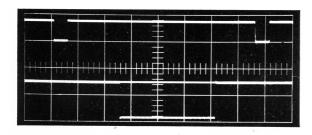

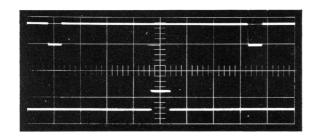

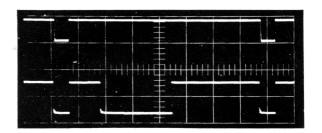

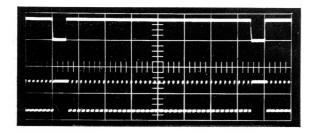

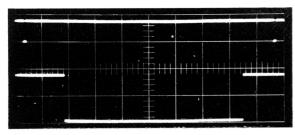

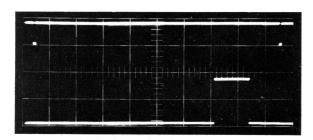

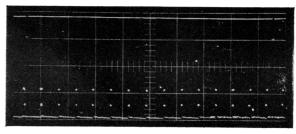

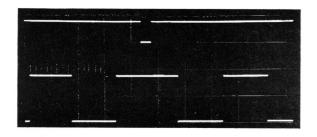

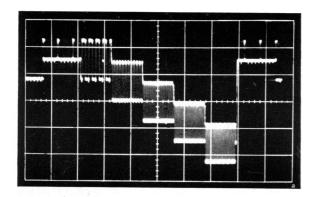

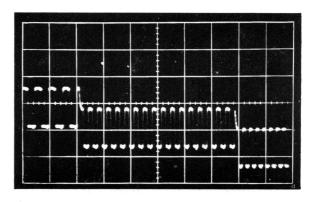

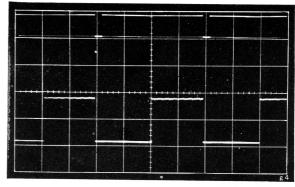

q1

2 V/cm 2 ms/cm reference: frame sync.

Fig. XIV-1 Oscilligrams, Unit 8

q2

2 V/cm 2 ms/cm reference: frame sync.

Fig. XIV-2 Pulse diagram for "q1"

Fig. XIV-3 Pulse diagram for "q2"

Fig. XIV-4 Pulse diagram for "i1"

Fig. XIV-5 Pulse diagram for "i2"

Unit 8

Gen for: i4

Unit 8 PEM 2917

PEM 2933

Fig. XIV-6 Pulse diagram for "i3"

Fig. XIV-7 Pulse diagram for "i4"

Fig. XIV-8 Pulse diagram for "i5"

Fig. XIV-9 Pulse diagram for "i6"

Gen for: i7

Unit 8

PEM2921

Fig. XIV-10 Pulse diagram for "i7"

i pulses in first and second field

Unit 8 PEM 2918

Fig. XIV-11 Arrangement of i-pulses

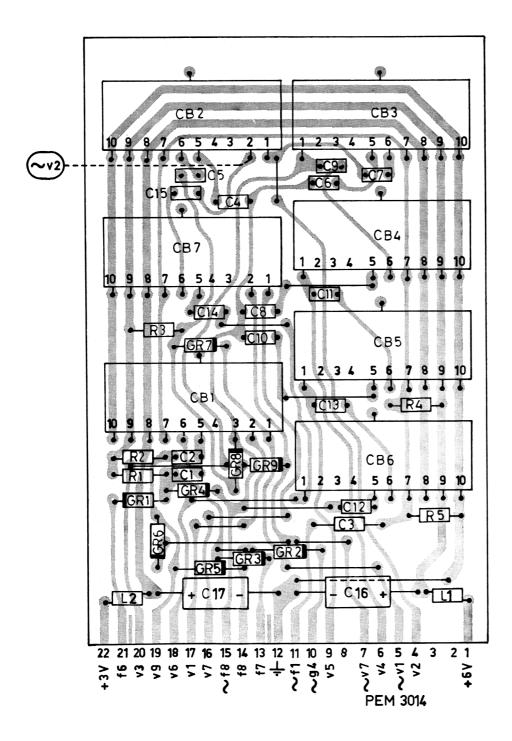

Fig. XIV-13 Printed wiring board, interval decoder, Unit 8

From version /06 TS8 - TS10 - TS12 - TS14 - TS16 and TS18 are of the type AC188 (4822 130 40456)

Fig. XIV-14 Circuit diagram, interval decoder, Unit 8

# XV Unit 9

#### The horizontal decoder

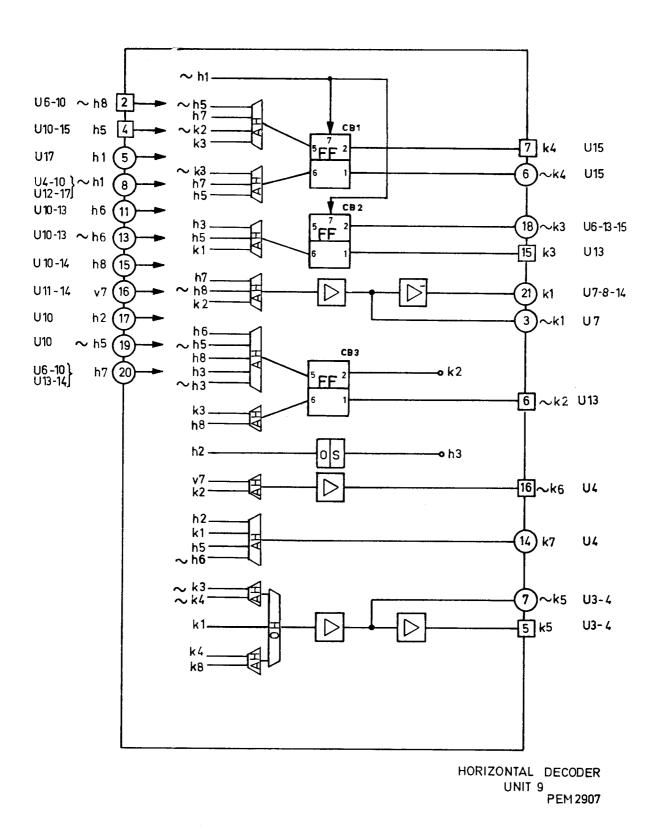

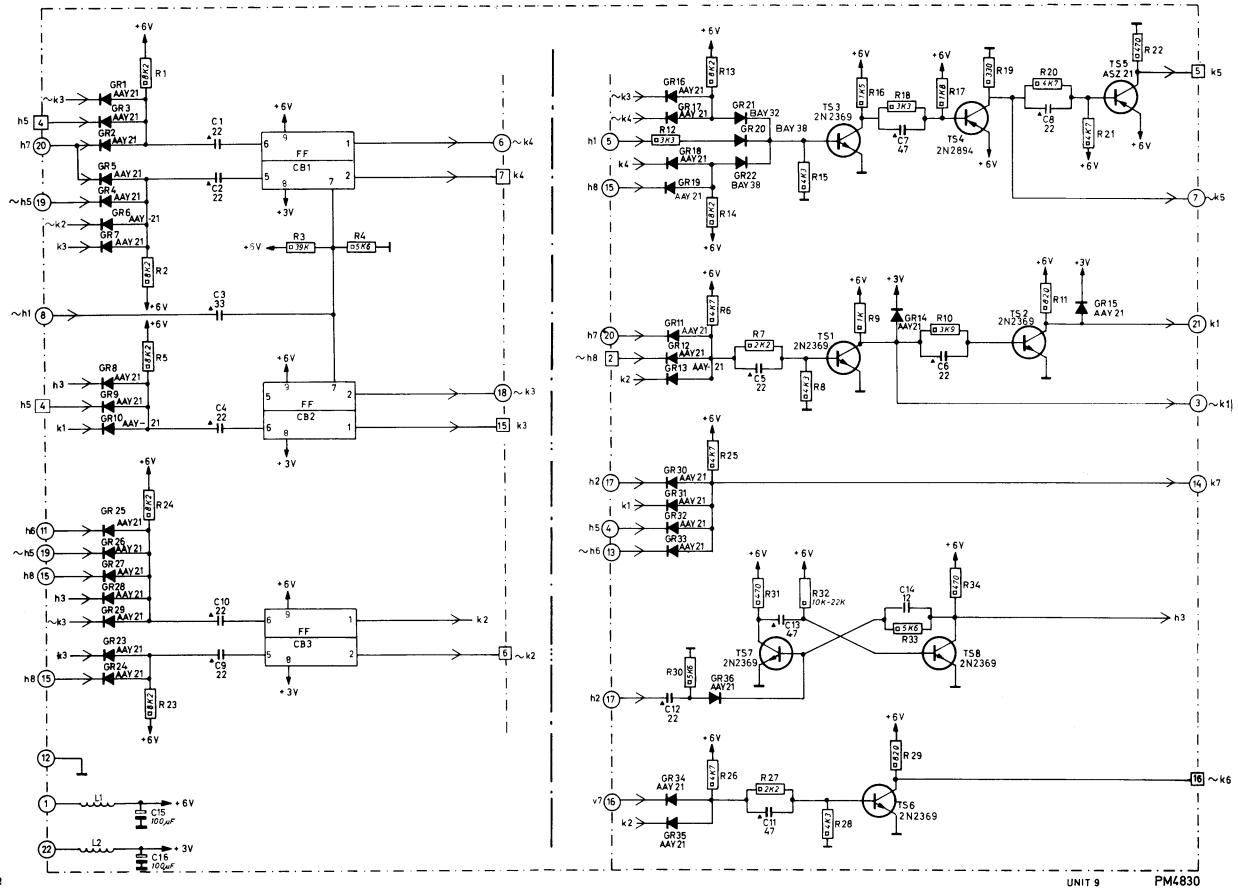

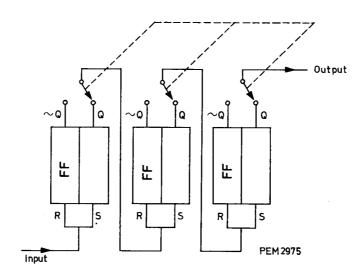

The purpose of the decoder is to supply horizontal gating pulses. These pulses, based on pulses from the horizontal divider (unit 10), are produced by a group of generators.

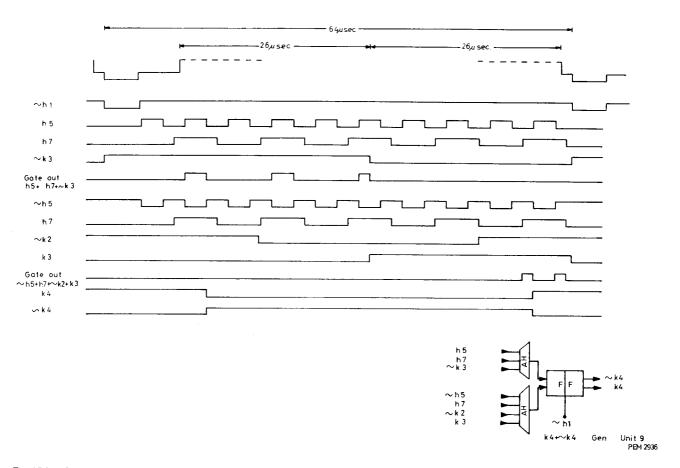

## Generator for the "k4" pulse

This generator consists of circuit block CB1 and the AND-gates GR1...GR3 and GR4...GR7.

In circumstances that the generator is not reset at the beginning of a line (eg. after switching) the " $\sim\,$ h1" pulse ensures that this will be done.

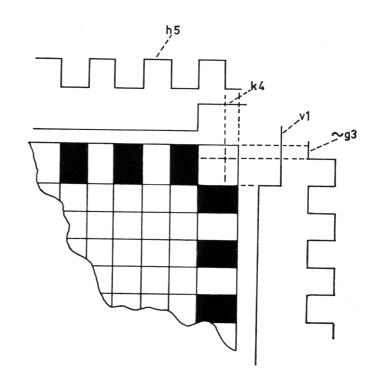

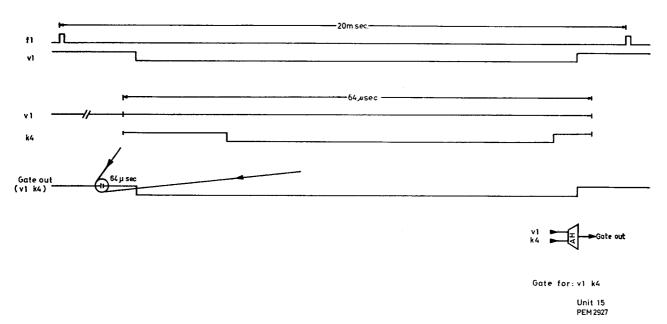

The generated "k4" and " $\sim$  k4" pulses are applied to the cross-bare gate (unit 15) where they determine the vertical borders of the crossed lines pattern (see Fig. XXII-1).

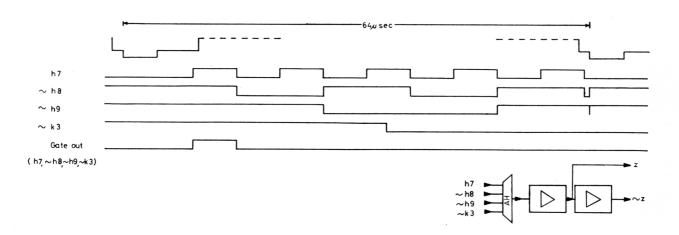

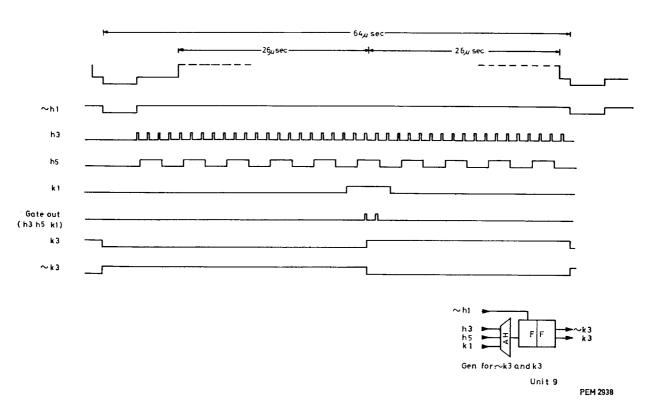

### Generator for the "k3" pulse

This generator consists of CB2 and GR8...GR10 and is set to zero for each line by the " $\sim$  h1" pulse; it is controlled by the "h3", "h5" and "k1" pulses.

The generated pulse ''k3'' is applied to unit 13 and the '' $\sim$  k3'' pulse to the units 6, 13 and 15.

These pulses produce the black/white steps in the top and bottom-segments of the circle (see Fig. XXII-1).

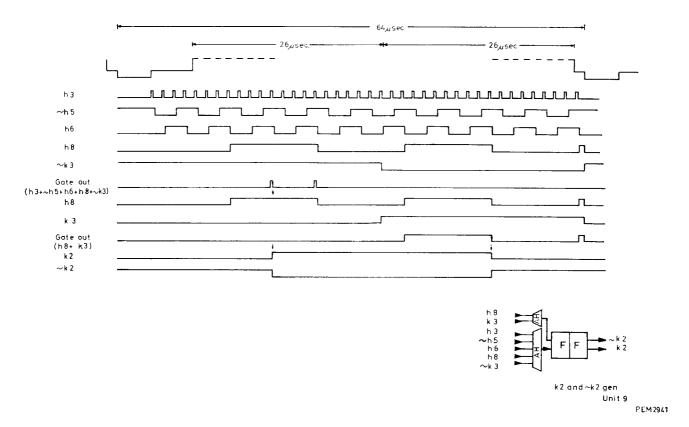

### Generator for the "k2" pulse

This generator consists of CB3 and the two AND-gates GR23, GR24 and GR25...GR29.

The generated pulse " $\sim$  k2" is applied to unit 13 and produces the wide black bar in the black/white steps pattern.

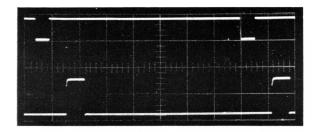

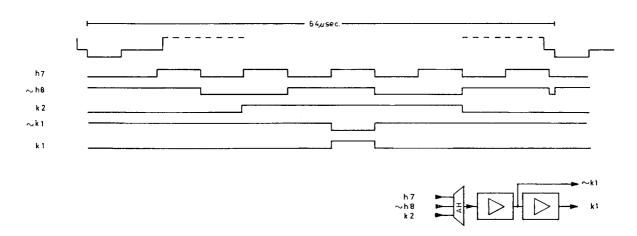

### Generator for the "k1" pulse

This generator consists of AND-gate GR11...GR13, amplifiers TS1...TS2, and clampers GR14 and GR15. It is controlled by the "h7", " $\sim$  h8" and "k2" pulses. TS2 is operating as an inverter while GR14...GR15 clamp the "k1" and " $\sim$ k1" pulses to +3 V. The

$^{\prime\prime}\sim$  k1" pulse is applied to unit 7, the "k1" pulse to units 7, 8 and 14.

In the last unit, the "k1" pulse helps producing the horizontal staircase signal as well as the definition lines in horizontal sequence.

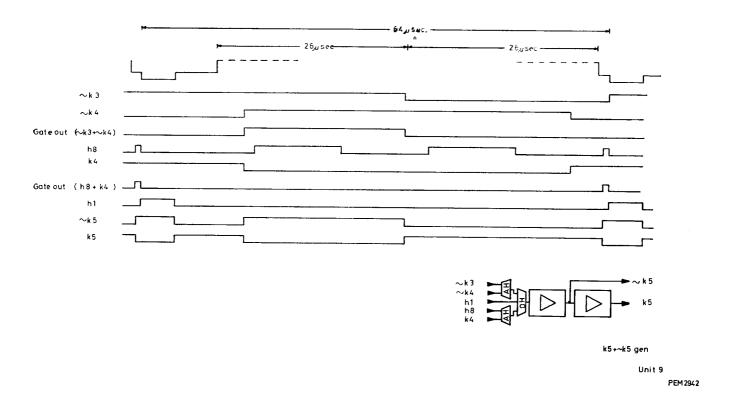

# Generator for the "k5" pulse

This generator, consisting of the AND-gates GR16... GR19, the OR-gate GR20... GR22 and the amplifiers TS3...TS5, is controlled by the "h1", "h8", " $\sim$  k3", "k4" and " $\sim$  k4" pulses. The pulses produced by the AND-gates are directed, via the OR-gate, to the amplifiers.

The generated pulses "k5" and " $\sim$  k5" are applied to units 3 and 4 and control the forward or- down-counting of the circle register.

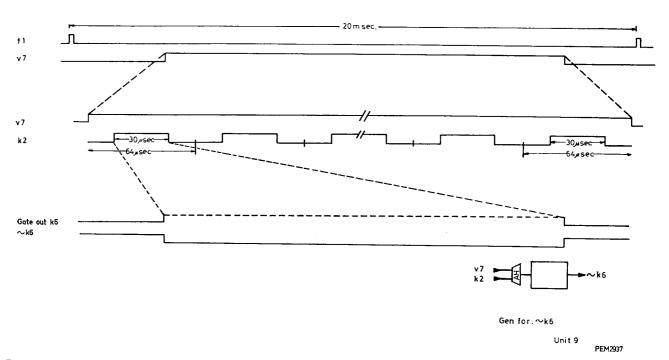

## Generator for the "k6" pulse

This generator, consisting of AND-gate GR34-GR35 and amplifier TS6, is controlled by the "k2" and "v7" pulses. The generated pulse " $\sim$  k6" is applied to unit 4 and determines "Start" of the clock-oscillator.

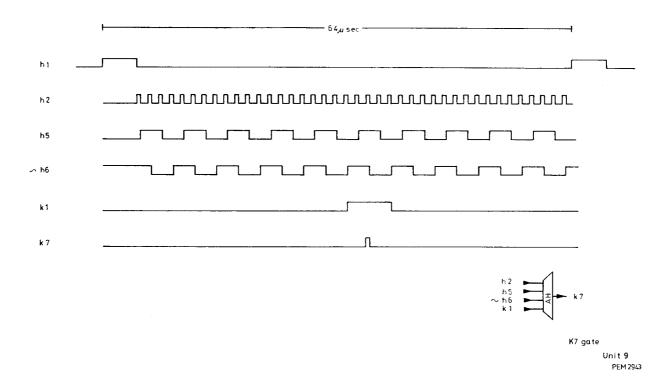

# Generator for the "k7" pulse

This generator consisting of AND-gate GR30... GR33, is controlled by the "h2", "h5", " $\sim$  h6" and "k1" pulses. The generated pulse "k7" is applied to unit 4 and determines "Stop" of the clock oscillator during reversal of the counting sense of the circle register (unit 3) in the middle of a line.

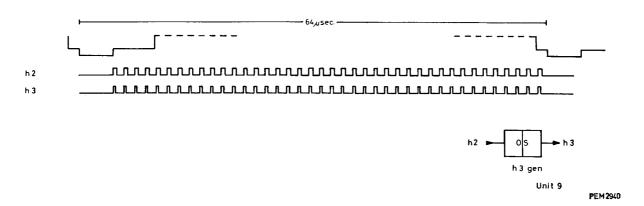

## Generator for the "h3" pulse

This generator (a one-shot multivibrator) consisting of GR36, TS7 and TS8. is controlled by the "h2" pulse. The generated pulse "h3", is applied to the generators producing the "k2" and "k3" pulses.

For checking and adjusting, see chapter X, units 3 and 4.

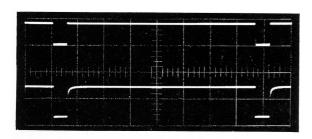

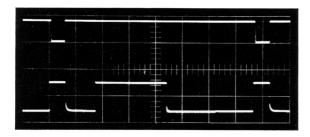

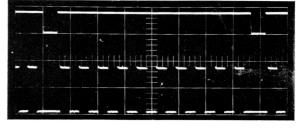

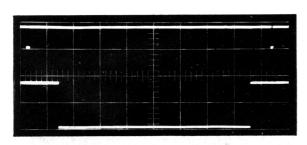

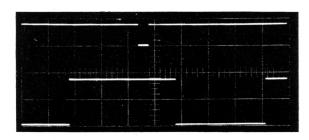

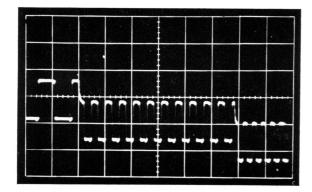

k1

5 V/cm 8 μs/cm

$\sim$  k2

2 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

$\sim$  k3

2 V/cm 8 μs/cm reference: line sync.

$\sim$  k4

2 V/cm  $10 \text{ }\mu\text{s/cm}$  reference: line sync.

k2

2 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

k3

2 V/cm 8  $\mu\text{s/cm}$  reference: line sync.

k4

2 V/cm  $10 \,\mu\text{s/cm}$  reference: line sync.

k5

5 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

$\sim$  k5

5 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

k7

1 V/cm 400 ns/cm

$\sim$  k6

1 V/cm  $8 \mu s/cm$  reference: line sync.

h3

$\begin{array}{ll} 5 \text{ V/cm} & 2 \text{ } \mu\text{s/cm} \\ \text{reference:} & \text{h2 pulse} \end{array}$

Fig. XV-2 Pulse diagrams for "k4" and "  $\sim$  k4"

Fig. XV-3 Pulse diagrams for "k3" and "  $\sim$  k3"

Fig. XV-4 Pulse diagrams for "k2" and " $\sim$  k2"

Fig. XV-5 Pulse diagrams for "k1" and "  $\sim$  k1"

Fig. XV-6 Pulse diagrams for "k5" and "  $\sim$  k5"

Fig. XV-7 Pulse diagram for " $\sim$  k6"

Fig. XV-8 Pulse diagram for "k7"

Fig. XV-9 Pulse diagram for "h3"

Fig. XV-10 Block-diagram, horizontal decoder, Unit 9

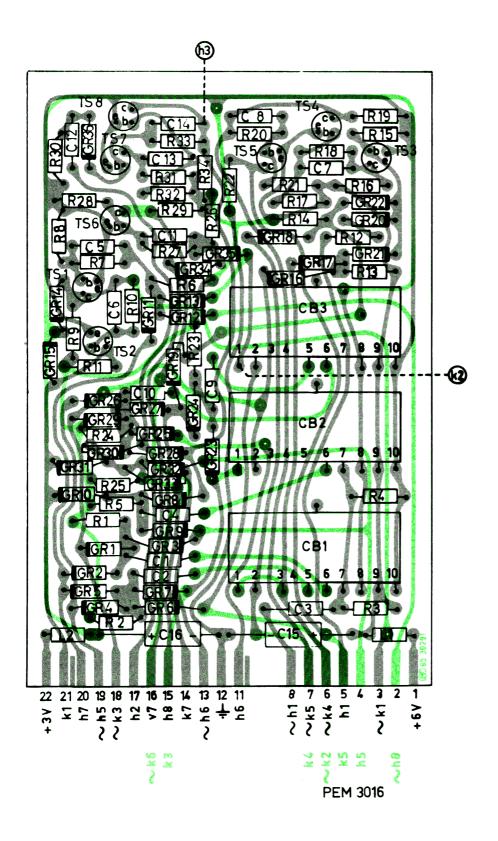

Fig. XV-11 Printed wiring board, horizontal decoder, Unit 9

Irratum: Range R32 should be  $6.8k\Omega$ -12k $\Omega$

Fig. XV-12 Circuit diagram, horizontal decoder. Unit 9

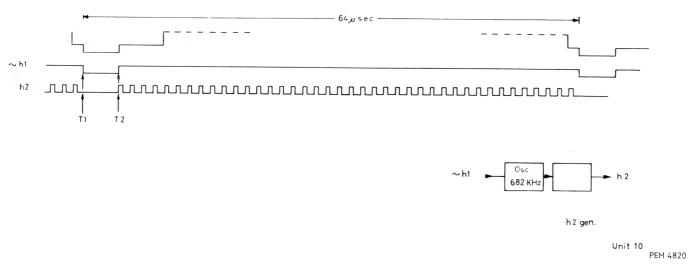

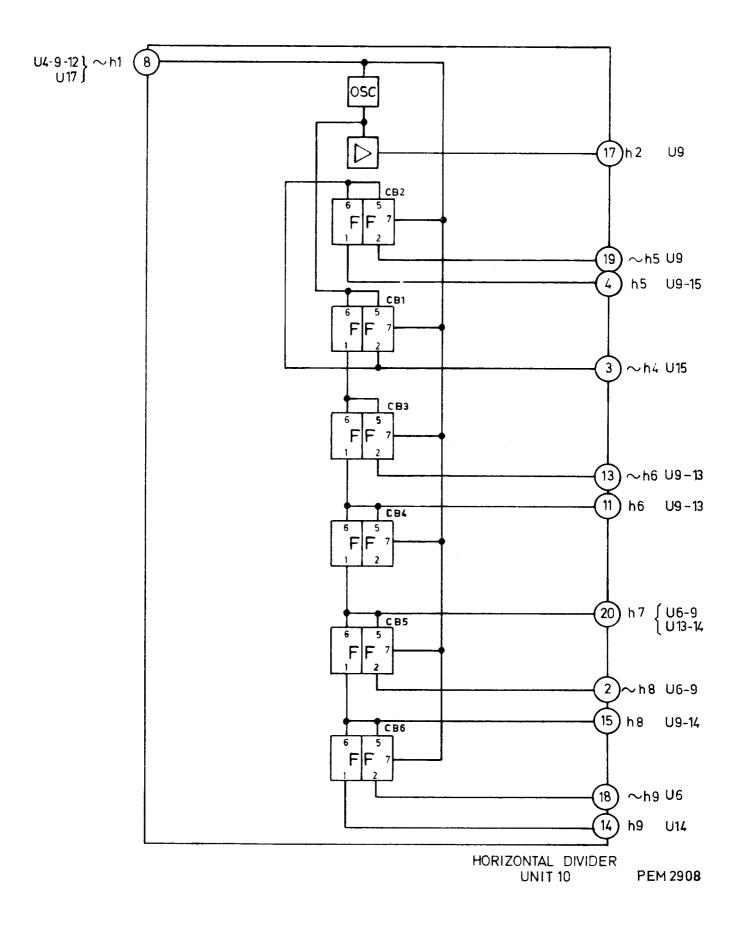

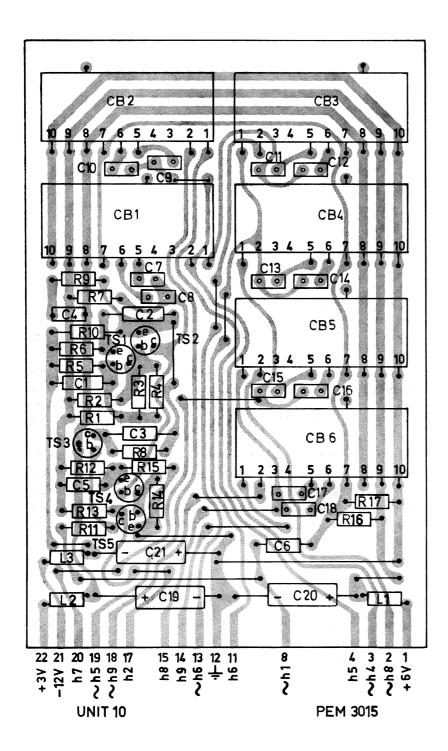

# XVI Unit 10

The horizontal divider

This circuit produces pulses to control a number of generators which compose the test patterns.

The circuit consists of a 5  $\pm$  1 stage binary divider CB1...CB6 and the 682 kHz¹) oscillator TS1 and TS2. The feedback of this oscillator is effected via C2, while the frequency is determined by R3 and R4. The oscillator is locked, via TS3, to the line frequency by the line pulse " $\sim$  h1".

During the negative " $\sim$  h1" pulse TS3 is saturated and TS2 is cut-of, causing the oscillator to stop. During the absence of the " $\sim$  h1" pulse TS3 is cut-of and the oscillator is operating.

The peaking circuitry R9-C4 is used for obtaining a correct pulse shape.

The oscillated pulses are applied to TS4 and TS5 and to the dividers CB1 . . . CB6. These dividers are set to zero for each line by means of the " $\sim h1$ " pulse via reset input 7, so that the generated pulses will have the same phase in all lines. The generated pulses "h2",

"h5", " $\sim$  h5", "h6", " $\sim$  h6", "h7", "h8" and " $\sim$  h8" arre applied to the horizontal decoder (unit 9), the "h7", " $\sim$  h8" and " $\sim$  h9" pulses to the line decoder (unit 6). The "h5" and " $\sim$  h4" pulses are also applied to the cross-bar gate (unit 15), the "h7", "h8" and "h9" pulses to the linear gate (unit 14) and the "h6", " $\sim$  h6" and "h7" pulses to the black/white step generator (unit 13).

#### Checking and adjusting

Measuring equipment:

Oscilloscope: e.g. PHILIPS PM 3330.

#### Frequency of horizontal oscillator (682 kHz)

Connect oscilloscope to "OUTPUT II".

The width of the black/white steps ("h5" pulse) at the left and right-hand side of the pattern should be 4.0  $\mu$ s for PM5540/E and 4.5  $\mu$ s for PM5540/A.

If not, select R4 (2.2 k $\Omega$  – 3.9 k $\Omega$ ).

## 1) For PM5540/A read: 687 kHz

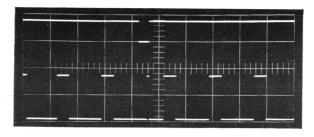

h2

$\begin{tabular}{ll} 5 \ V/cm & 8 \ \mu s/cm \\ \hline reference: line sync. \\ \end{tabular}$

h4

2 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

$\sim {\rm h4}$

2 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

h5

2 V/cm 8  $\mu\text{s/cm}$  reference: line sync.

$\sim$  h5

2 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

h6

2 V/cm  $8 \mu \text{s/cm}$  reference: line sync.

$\sim$  h6

$2 \ \text{V/cm} \qquad 8 \ \mu \text{s/cm}$  reference: line sync.

h7

2 V/cm  $8 \mu \text{s/cm}$  reference: line sync.

h8

2 V/cm  $8 \mu\text{s/cm}$  reference: line sync.

$\sim$  h8

$2 \ \text{V/cm} \qquad 8 \ \mu \text{s/cm}$  reference: line sync.

h9

2 V/cm  $8~\mu s/cm$ reference: line sync.

$\sim$  h9

2 V/cm  $8 \, \mu s/cm$ reference: line sync.

Fig. XVI-2 Pulse diagram for "h2"

Fig. XVI-3 Pulse diagrams for " $\sim$  h4", "h5" and " $\sim$  5"

Fig. XVI-4 Pulse diagrams for "h6" . . . "h9"

Fig. XVI-7 Circuit diagram, horizontal divider, Unit 10

# XVII Unit 11

#### The vertical decoder

The purpose of the decoder is to supply the vertical gating pulses. These pulses, based on pulses from the vertical divider (unit 12), are produced by a group of generators.

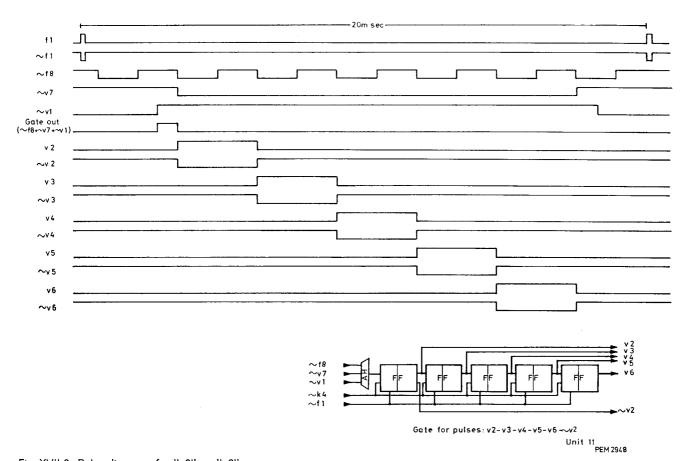

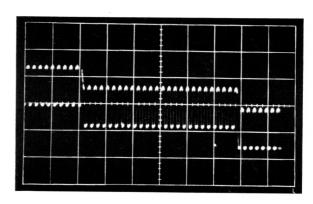

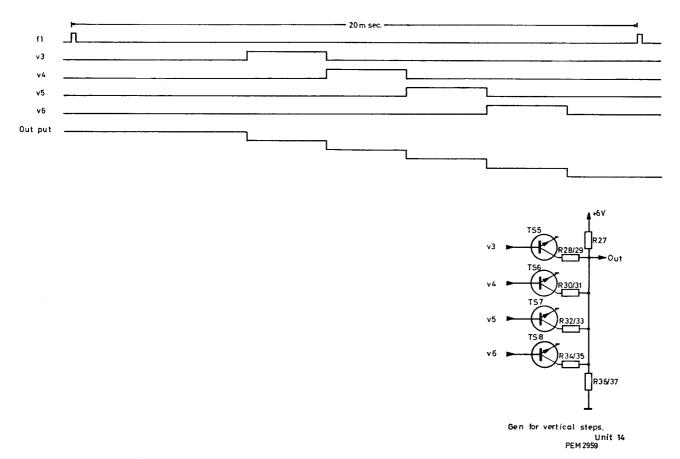

# Generator for the "v2", "v3", "v4", "v5" and "v6" pulses

The pulses are produced in the flip-flops CB2...CB6 which function as a shift register.

First all flip-flops are set to zero by the " $\sim$  f1" pulse.

Then the " $\sim$ f8" pulse is applied to input 5, but as these flip-flops are set to zero, they are not influenced by the " $\sim$ f8" pulse. Due to the action of the combined pulses " $\sim$ v1", " $\sim$ f8" and " $\sim$ v7" in the AND-gates GR7 . . . GR9, flip flop CB2 changes from state "0" to state "1".

When the first negative step of the " $\sim$  f8" pulse appears, CB2 changes into the other stable state. At the next negative step of the " $\sim$  f8" pulse CB8 changes, etc. so that the information of each flip-flop shifts one place upwards, untill they all in turn are activated.

The generated pulses "v2"..."v6" are applied to the interval decoder (unit 8), the "v2", "v4" and "v6" pulses to the black/white step generator (unit 13) and "v3", "v4", "v5" and "v6" pulses to the linear-gate (unit 14). The "v4" pulse is also applied to the "g4" and " $\sim$  g4" generator in unit 17.

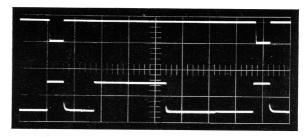

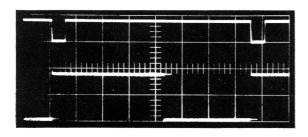

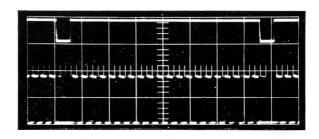

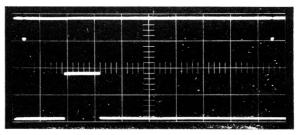

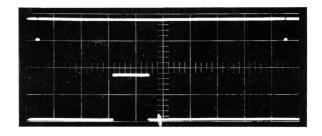

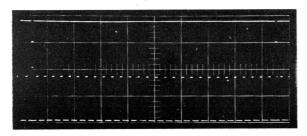

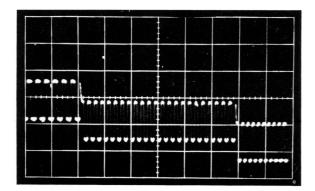

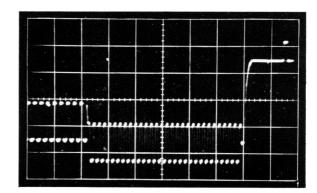

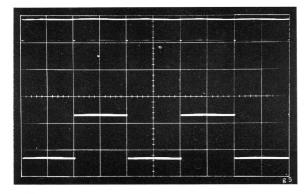

v1

2 V/cm 2 ms/cm reference: frame sync.

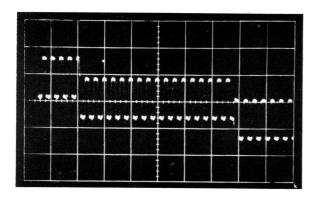

Fig. XVII-1 Oscillograms, Unit 11

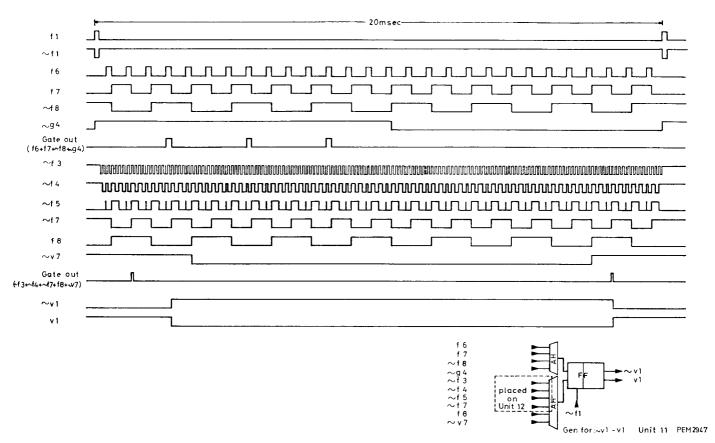

#### Generator for the "v1" pulse

This generator consists of the flip-flop CB1, the AND-gate GR1...GR4 and GR5...GR6 combined with GR11...GR14 (unit 12) producing the "v9" pulse.

The "reset" of CB1 (input 6) is controlled by the gate output pulses of GR1 . . . GR4 ("f6", "f7", " $\sim$  f8" and " $\sim$  g4"), and "set" (input 5) by the output pulses of GR5 . . . GR6 and GR11 . . . GR14 "f8", " $\sim$  v7" and "v9" ("v9" = " $\sim$  f3", " $\sim$  f4", " $\sim$  f5" and " $\sim$  f7").

In circumstances that the generator is not reset at the beginning of a field (e.g. after switching) the " $\sim$  f1" pulse ensures that this will be done. The gate output pulse on input 5 cannot trigger the flip-flop. When the first negative step appears at input 6, flip-flop changes its state until the next negative step at input 5 causes the flip-flop to change its state again.

The "v1" and " $\sim$  v1" pulses are applied to the Crossbar gate (unit 15).

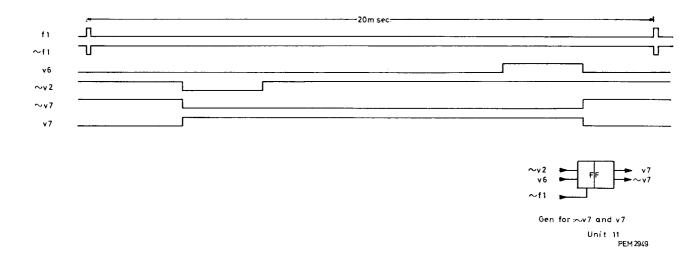

#### Generator for the "v7" pulse

The "v7" and " $\sim$  v7" pulses are produced by flip-flop CB7 of which the "set" and "reset" inputs are controlled by the " $\sim$  v2" and "v6" pulses. In circumstances that the generator is not reset at the beginning of a field (e.g. after-switching), the " $\sim$  f1" pulse ensures that this will be done. The "v7" pulse is applied to units 9 and 14 and the " $\sim$  v7" pulse to units 8 and 13.

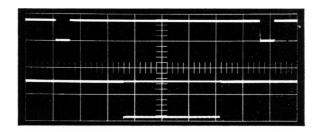

v2

2 V/cm 2 ms/cm reference: frame sync.

$\sim$  v2

2 V/cm 2 ms/cm reference: frame sync.

v4

2 V/cm 2 ms/cm reference: frame sync.

v6

2 V/cm 2 ms/cm reference: frame sync.

$\sim$  v7

2 V/cm 2 ms/cm reference: frame sync.

v3

2 V/cm 2 ms/cm reference: frame sync.

v5

2 V/cm 2 ms/cm reference: frame sync.

v7

2 V/cm 2 ms/cm reference: frame sync.

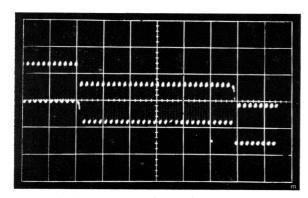

Fig. XVII-2 Pulse diagrams for "v1" and " $\sim$  v1"

Fig. XVII-3 Pulse diagrams for "v2" . . . "v6"

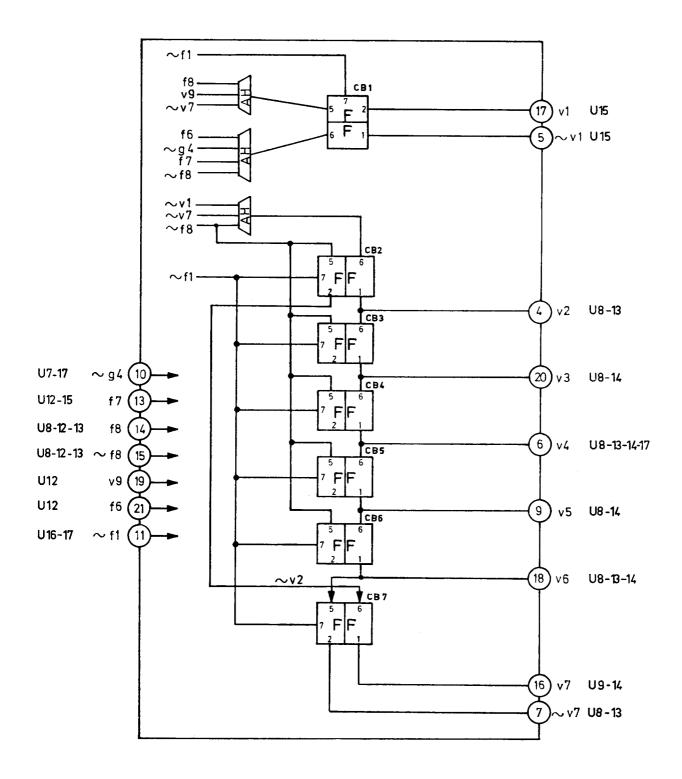

Fig. XVII-7 Circuit diagram, vertical decoder, Unit 11

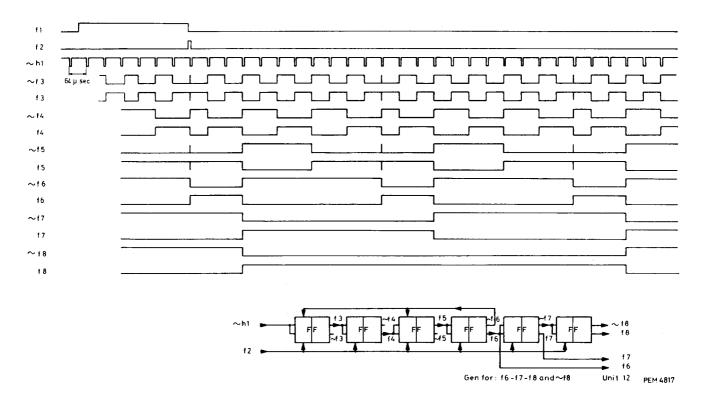

# XVIII Unit 12

The vertical divider

This circuit produces pulses which, after decoding drive a number of generators used to generate the gating pulses for the test patterns.

The circuit is built up as a 6 stage divider which counts pulses of the line frequency (" $\sim$  h1").

The flip-flops CB1...CB4 form a 11:1¹) divider by feeding back the " $\sim$  f6" pulse to CB1 and CB3. Flip-flop CB5 produces the "f7" pulse which is repeated every 22 lines. Flip-flop CB6 produces the "f8" pulse which, in combination with the gate pulses of units 8 and 13, is used for dividing the circle into 10 intervals. To get the pulses in the correct mutual phase, the divider is set each frame by the "f2" pulse, after the

$^{\prime\prime}\sim$  h1" pulse, present at the same time, has disappeared.

CB1, 2, 4, 5 and 6 are set to state "0" while CB3 is set to state "1".

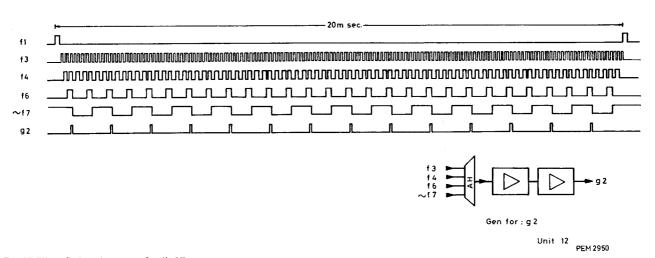

#### Generator for the "g2" pulse

This generator, which supplies the "g2" pulse, consists of the AND-gate GR7-GR10 and the amplifier TS1... TS2. This pulse, which is clamped to +3 V by GR19, is applied to the units 7, 8 and 17.

The AND-gate GR11...GR14, supplying the "v9" pulse is used in unit 11.

The AND-gate GR15...GR18, supplying the "v8" pulse is used in unit 15.

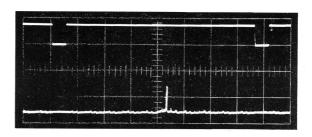

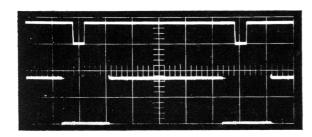

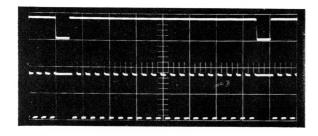

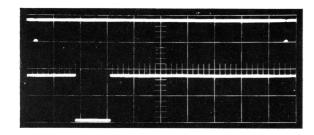

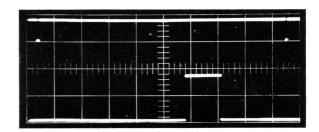

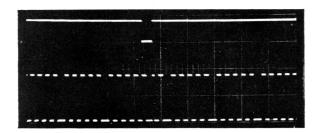

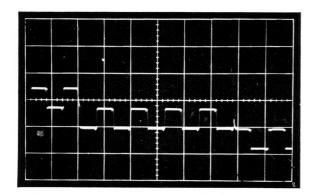

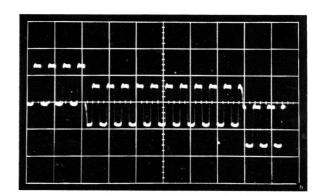

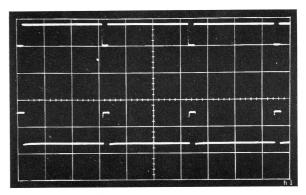

g2

5 V/cm 2 ms/cm reference: frame sync.

v8

2 V/cm 2 ms/cm reference: frame sync.

v9

2 V/cm 2 ms/cm reference: frame sync.

f3

2 V/cm 400  $\mu\text{s/cm}$  reference: frame sync.

$\sim$  f3

2 V/cm 400  $\mu\text{s/cm}$  reference: frame sync.

$\sim$  f4

2 V/cm 400 μs/cm reference: frame sync.

f4

2 V/cm 400  $\mu\text{s/cm}$  reference: frame sync.

f5

2 V/cm 400  $\mu\text{s/cm}$  reference: frame sync.

$\sim$  f5

2 V/cm 400  $\mu\text{s/cm}$  reference: frame sync.

$\sim$  f6

2 V/cm  $400 \,\mu\text{s/cm}$  reference: frame sync.

$\sim$  f7

2 V/cm 400 μs/cm reference: frame sync.

$\sim$  f8

2 V/cm  $400 \,\mu\text{s/cm}$  reference: frame sync.

f6

2 V/cm 400  $\mu\text{s/cm}$  reference: frame sync.